# 16nm 64Gb e-NAND Product Family

# **Revision History**

| Revision NO. | History                                                                                                | Draft Date    | Remark |

|--------------|--------------------------------------------------------------------------------------------------------|---------------|--------|

| 0.0          | Preliminary                                                                                            | 03, Sep, 2013 |        |

| 0.1          | Updated Bus timing in HS400 mode                                                                       | 24, Oct, 2014 |        |

| 0.2          | Updated Register value                                                                                 | 12, Nov, 2014 |        |

| 0.3          | Updated eMMC5.0 Connection guide [P61_Connection guide]                                                | 10, Dec, 2014 |        |

| 0.4          | Updated tPre/tPost-Amble [p35_HS 400 Device out put timing]                                            | 12, Dec, 2014 |        |

| 0.5          | Revised HPI Time out Updated time out value [p28_Timings] Updated register value [54_Extended CSD_198] | 20, Dec, 2014 |        |

# **Table of Contents**

| 1. Device Summary                                              | 5  |

|----------------------------------------------------------------|----|

| 2. Features                                                    | 5  |

| 3. Description                                                 | 6  |

| 3.1 e-NAND Standard Specification                              | 6  |

| 4. Device Physical Description                                 |    |

| 4.1 Package Connections                                        |    |

| 4.2 Form Factor                                                |    |

| 4.3 PKG Mechanical Drawing                                     |    |

| 4.3.1 11.5x13.0x0.8                                            |    |

| 4.3.2 11.5x13.0x1.0                                            |    |

| 4.3.3 11.5x13.0x1.2                                            |    |

| 5. e-NAND Features                                             | 14 |

| 5.1 Bus Modes                                                  |    |

|                                                                |    |

| 5.2 User Density                                               |    |

| 5.3 Write Endurance<br>5.4 Boot Operation                      |    |

| 5.5 Power Modes                                                |    |

| 5.5.1 e-NAND Power-Up Guidelines                               |    |

| 5.5.2 e-NAND Power Cycling                                     |    |

| 5.5.3 Leakage                                                  |    |

| 5.5.4 Power Supply                                             |    |

| 5.5.5 Active Power consumption                                 |    |

| 5.5.6 Low Power Mode                                           |    |

| 5.6 Erase Write Protect Group Size                             |    |

| 5.7 Timings                                                    |    |

| 5.7.1 Time Out                                                 |    |

| 5.7.2 Bus Timing                                               |    |

| 5.7.3 Bus Timing for DAT Signals During 2X Data Rate Operation |    |

| 5.7.4 Bus Timing Specifiaction in HS400 mode                   |    |

| 5.8 Bus Signal                                                 |    |

| 5.8.1 Bus Signal Line Load                                     |    |

| 5.8.2 Overshoot / Under shoot specification                    |    |

| 5 9 Performance                                                | 41 |

| 6. Commands                              | 42 |

|------------------------------------------|----|

| 6.1 Command Classes                      | 42 |

| 6.2 Detailed Command Description         | 43 |

| 7. Device Registers                      | 50 |

| 7.1 Operation Conditions Register (OCR)  | 50 |

| 7.2 Card Identification (CID) Register   | 51 |

| 7.3 Card Specific Data Register(CSD)     | 52 |

| 7.4 Extended CSD Register                | 54 |

| 7.5 RCA (Relative Card Address)          | 60 |

| 7.6 DSR (Driver Stage Register) Register | 60 |

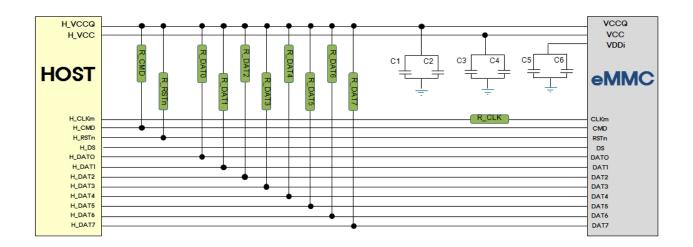

| 8. Connection Guide                      | 61 |

# 1. Device summary

| Density | NAND      | Root Part Number | Package | PKG size (mm) |

|---------|-----------|------------------|---------|---------------|

| 8GB     | 16nm 64Gb | H26M41103HPR     | FBGA153 | 11.5x13x0.8   |

| 16GB    | 16nm 64Gb | H26M52103FMR     | FBGA153 | 11.5x13x1.0   |

| 32GB    | 16nm 64Gb | H26M64103EMR     | FBGA153 | 11.5x13x1.0   |

| 64GB    | 16nm 64Gb | H26M78103CCR     | FBGA153 | 11.5x13x1.2   |

#### 2. Features

- · Packaged NAND flash memory with MultiMediaCard interface

- · High capacity memory access

- e-NAND system specification, compliant with V5.0

- Full backward compatibility with previous e-NAND system specification (MMC 4.5)

- Bus mode

- High-speed eMMC protocol.

- Three different data bus widths: 1 bit(default), 4 bits, 8 bits

- Data transfer rate: up to 400Mbyte/s (HS400)

- DDR mode supported (Up to 400MB/s, 200MHz, DDR Mode)

- Operating voltage range VCC(NAND): 2.7 - 3.6V

VCCQ(Controller): 1.7 - 1.95V / 2.7 - 3.6V

- · Error free memory access

- Error correction code (ECC)

- Internal enhanced data management algorithm (Wear levelling, Bad block management, Garbage collection)

- Possibility for the host to make sudden power failure safe-update operations for data content

- Hardware & Software reset supported

- Security

- Secure Erase

- Secure Trim

- Write Protection

- Sanitize

- eDrive

- RPMB

- Boot

- Normal / Alternative boot sequence method

- Power saving

- Enhanced power saving method by introducing sleep functionality

- Partition management with enhanced storage.

- Performance

- HS400

- Power off Notification

- Context ID

- Packed CMD

- Discard

- Cache

- Data tag

- Maintenance

- Health Report

- Field Firmware Update

- Product State Awareness

- Power Off Notification Sleep Clarification

- HPI

• Temperature Operation (-25  $^{\circ}$  ~ +85  $^{\circ}$ ), Storage without operation (-40  $^{\circ}$  ~ 85  $^{\circ}$ )

\* This Product in compliance with the RoHS directive.

# 3. Description

e-NAND is an embedded flash memory storage solution. e-NAND was developed for universal low cost data storage and communication media. e-NAND is fully compatible with MMC bus and host.

e-NAND communications are made through an advanced 13-pin bus, and it can be either 1-bit, 4-bit, or 8-bit in width. e-NAND operates in high-speed mode at clock frequencies equal or higher than 20MHz as defined in the MMC JEDEC standard. The communication protocol is defined in this MMC JEDEC standard.

e-NAND is designed to cover a wide area of applications such as smart phones, tablet PC, cameras, PDA, digital recorders, MP3 players, electronic toys, etc. Features are mainly high speed performance, low power consumption, low cost and high density.

To meet the requirements of embedded high density storage media and mobile applications, e-NAND supports 3.3V for VCC, and 3.3V or 1.8V for VCCQ. The address argument for e-NAND is consistent with 512-byte sector addressing rather than byte addressing. This means that e-NAND is not capable of supporting backward compatibility with devices using byte addressing(typically devices that have maximum capacity less that 2 Gigabytes). If the e-NAND receives byte addressing, then the e-NAND will change its state to inactive.

e-NAND has the built-in intelligent controller which manages interface protocols, Wear Leveling, Bad Block Management, Garbage Collection, and ECC. e-NAND protects the data contents from the host sudden power off failure by safe-update operations with reliable write features. The device supports a boot operation with enhance area and sleep/awake commands. In particular, the host power regulator for VCC can minimize the power consumption during the sleep state.

#### 3.1 e-NAND standard specification

e-NAND device is fully compatible with the JEDEC Standard Specification No. JESD84-B50. This data sheet describes the key and specific features of e-NAND. Any additional interface related information, the device to a host system, and all other practical methods for card detection/access can be found in the proper section of the JEDEC Standard Specification.

# 4. Device Physical Description

# 4.1 Package Connections

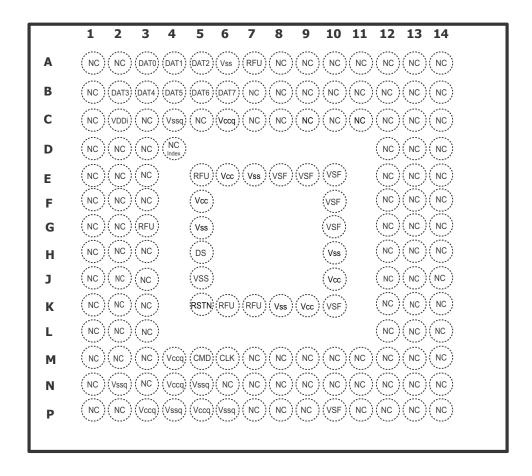

Figure 1: FBGA153 Package Connections (Top view through package)

Table 1 : FBGA153 Ball Description

| Ball NO                       | Symbol     | Туре    | Ball Function                                                                                                                                                                                     |

|-------------------------------|------------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| M6                            | CLK        | Input   | Clock:<br>Each cycle directs a 1-bit transfer on the<br>command and DAT lines.                                                                                                                    |

| M5                            | CMD        | Input   | Command: A bidirectional channel used for device initialization and command transfers. Command has two operating modes: 1) Open-Drain for initialization. 2) Push-Pull for fast command transfer. |

| А3                            | DAT0       | I/O     | Data I/O0:<br>Bidirectional channel used for data transfer.                                                                                                                                       |

| A4                            | DAT1       | I/O     | Data I/O1:<br>Bidirectional channel used for data transfer.                                                                                                                                       |

| A5                            | DAT2       | I/O     | Data I/O2:<br>Bidirectional channel used for data transfer.                                                                                                                                       |

| B2                            | DAT3       | I/O     | Data I/O3:<br>Bidirectional channel used for data transfer.                                                                                                                                       |

| В3                            | DAT4       | I/O     | Data I/O4:<br>Bidirectional channel used for data transfer.                                                                                                                                       |

| B4                            | DAT5       | I/O     | Data I/O5:<br>Bidirectional channel used for data transfer.                                                                                                                                       |

| B5                            | DAT6       | I/O     | Data I/O6:<br>Bidirectional channel used for data transfer.                                                                                                                                       |

| B6                            | DAT7       | I/O     | Data I/O7:<br>Bidirectional channel used for data transfer.                                                                                                                                       |

| K5                            | RST_n      | Input   | Reset signal pin                                                                                                                                                                                  |

| E6,F5,J10,K9                  | VCC        | Supply  | VCC:<br>Flash memory I/F and Flash memory power<br>supply.                                                                                                                                        |

| C6, M4, N4, P3, P5            | VCCQ       | Supply  | VCCQ: Memory controller core and MMC interface I/O power supply.                                                                                                                                  |

| A6, E7, G5, H10, J5,<br>K8    | Vss        | Supply  | Vss:<br>Flash memory I/F and Flash memory ground<br>connection.                                                                                                                                   |

| C4, N2, N5, P4, P6            | Vssq       | Supply  | Vssq:<br>Memory controller core and MMC I/F ground<br>connection                                                                                                                                  |

| C2                            | VDDi       |         | VDDi:<br>Connect 0.1uF capacitor from VDDi to ground.                                                                                                                                             |

| H5                            | DS         | Out put | DS : Data Strobe                                                                                                                                                                                  |

| E8, E9, E10, F10,<br>G10, K10 | VSF Supply |         | VSF : Vendor specific Function<br>SK hynix use E8, E9 Pin as VSF Pin                                                                                                                              |

| RFU                           |            |         | Reserved for future use                                                                                                                                                                           |

# 4.2 Form Factor

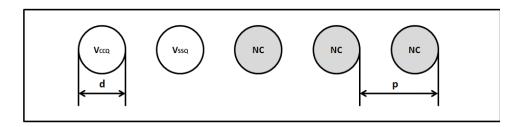

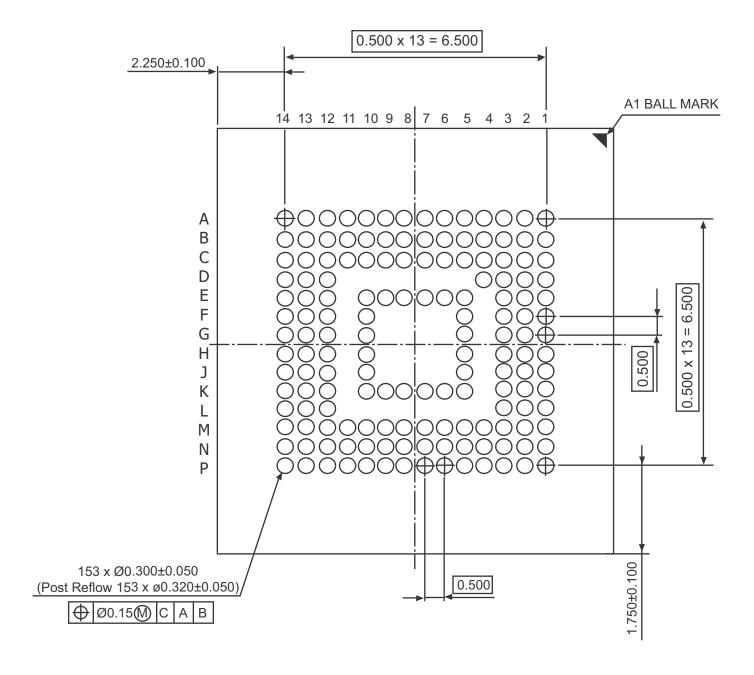

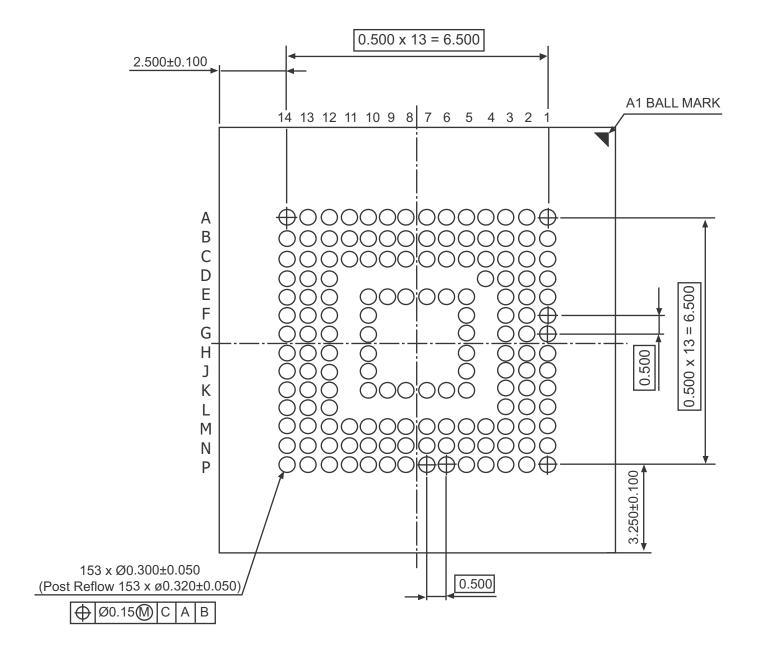

The ball diameter, d, and the ball pitch, p, for the FBGA153 package are • d = 0.30mm (solder ball diameter) • p = 0.5mm (ball pitch)

Figure 2: e-NAND ball diameter and pitch

# 4.3 PKG mechanical drawing

# 4.3.1 11.5mm x13.0mm x0.8mm Package Dimension

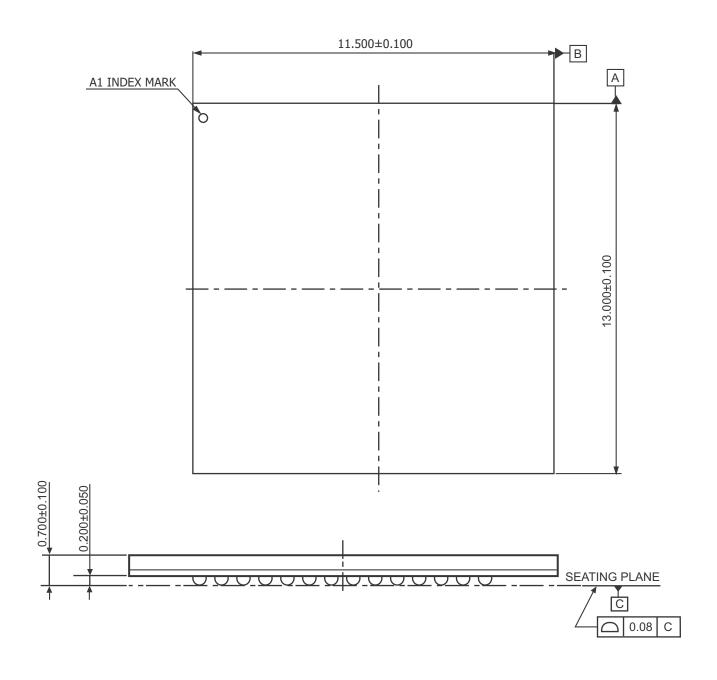

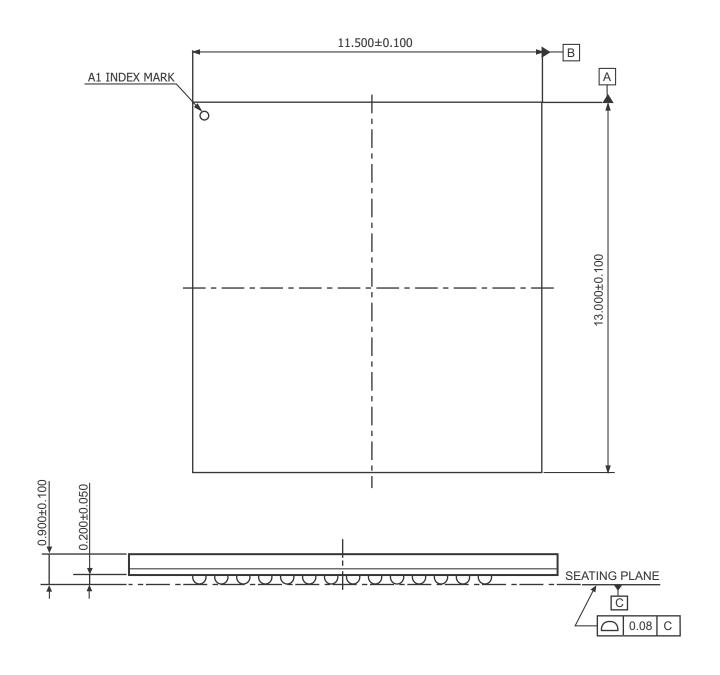

Figure 3: 11.5x13.0x0.8 Top & Side View

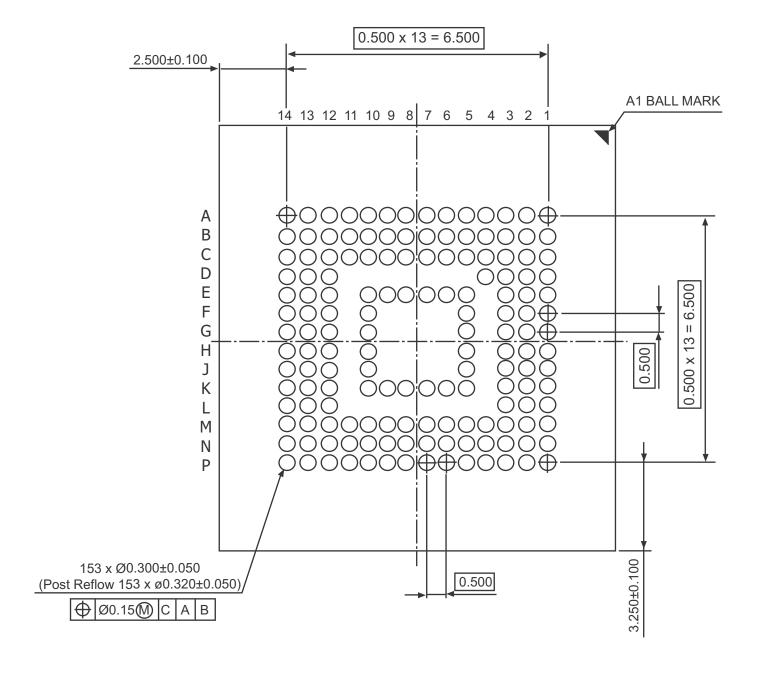

Figure 4: 11.5x13.0x0.8 Bottom View

# 4.3.2 11.5mm x13.0mm x1.0mm Package Dimension

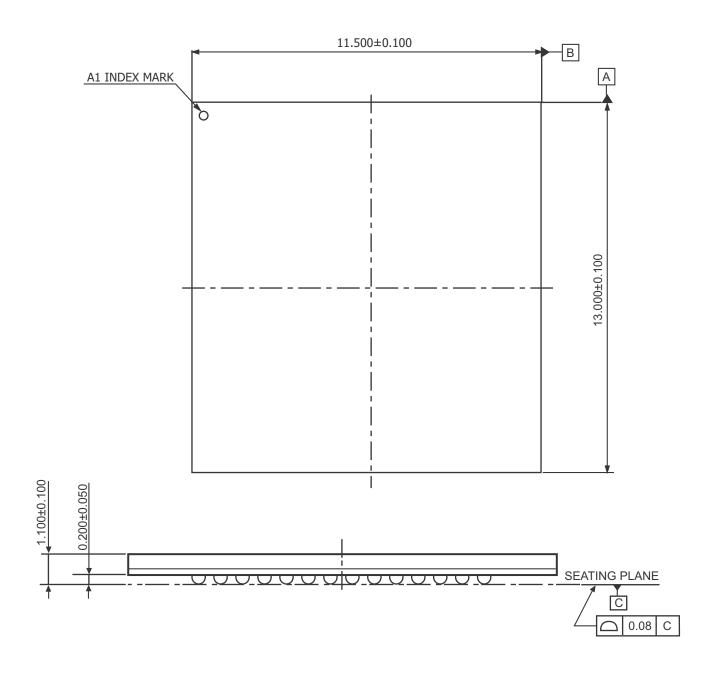

Figure 5: 11.5x13.0x1.0 Top & Side View

Figure 6: 11.5x13.0x1.0 Bottom View

# 4.3.3 11.5mm x13.0mm x1.2mm Package Dimension

Figure 7: 11.5x13.0x1.2 Top & Side View

Figure 8: 11.5x13.0x1.2 Bottom View

#### 5. e-NAND Features

#### 5.1 Bus Modes

#### • Boot mode

e-NAND will be in boot mode after power cycle, reception of CMD0 with argument of 0xF0F0F0F0 or assertion of hardware reset signal.

#### • Identification Mode

e-NAND will be in identification mode when boot operation mode is finished or if host does not support a boot operation mode. e-NAND will be in this mode until the SET\_RELATIVE\_ADDR command (CMD3) is received.

#### • Interrupt Mode

e-NAND support Interrupt Mode. Host and device enter and exit interrupt mode simultaneously. In interrupt mode there is no data transfer. The only message allowed is an interrupt service request from the device or the host.

#### • Data Transfer Mode

e-NAND will enter Data Transfer Mode once RCA is assigned to it. The host will enter Data Transfer Mode after identifying e-NAND on the bus.

#### Inactive Mode

e-NAND will enter to inactive mode when e-NAND is operating invalid voltage range or access mode. Also e-NAND can be set to inactive mode by Go\_INACTIVE\_STATE command (CMD15). e-NAND can change from inactive mode to Pre-idle state by reset.

Table 2: Bus modes overview

| e-NAND state         | Operation mode        | Bus mode   |  |

|----------------------|-----------------------|------------|--|

| Inactive state       | Inactive Mode         |            |  |

| Pre-Idle state       | Boot Mode             |            |  |

| Pre-Boot state       | BOOL Mode             | Open-Drain |  |

| Idle state           |                       | ·          |  |

| Ready state          | Identification Mode   |            |  |

| Identification state |                       |            |  |

| Stand-by state       |                       |            |  |

| Sleep state          |                       |            |  |

| Transfer state       |                       |            |  |

| Bus-Test state       | Data Transfer Mode    |            |  |

| Sending-data state   | - Data Transfer Plode | Push-Pull  |  |

| Receive-data state   |                       |            |  |

| Programming state    |                       |            |  |

| Disconnect state     |                       |            |  |

| Boot state           | Boot Mode             |            |  |

| Wait-IRQ State       | Interrupt mode        | Open-drain |  |

### 5.2 User Density

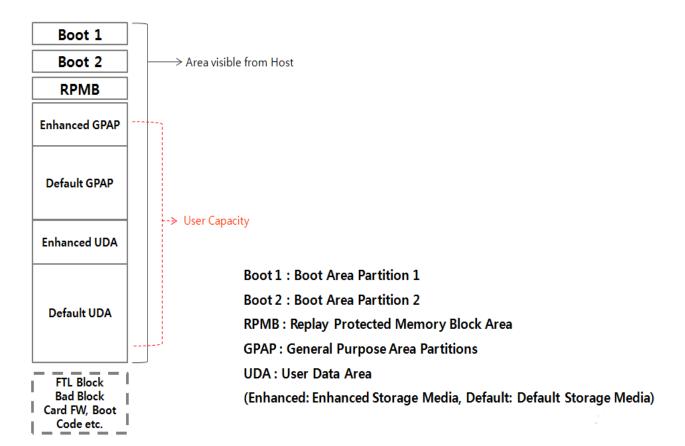

Figure 9: Partition diagram

# ■ Partition size (Boot , RPMB)

| 5       | 5 15 1111 10       | RPMB   |                                                        |                          | RPMB |  |  |

|---------|--------------------|--------|--------------------------------------------------------|--------------------------|------|--|--|

| Denisty | Boot Partition 1,2 | size   | Perfor                                                 | mance                    |      |  |  |

| 8GB     |                    |        |                                                        |                          |      |  |  |

| 16GB    |                    |        |                                                        |                          |      |  |  |

| 32 GB   | 4096KB             | 4096KB | Sequential. Read : 20MB/s<br>Sequential. Write : 5MB/s | Data transfer unit : 8KB |      |  |  |

| 64 GB   |                    |        |                                                        |                          |      |  |  |

Note: RPMB is implemented oprating with sector unit. About RPMB data transfer unit, refer to the EXT\_CSD REL\_WR\_SEC\_C [222] value. It is highly recommended to use 8KB data transfer unit to maximize access performance to RPMB area.

#### ■ User Density Size

| Capacity | LBA(Hex)  | LBA(Dec)    | Capacity(Bytes) |

|----------|-----------|-------------|-----------------|

| 8GB      | 0xE90000  | 15,269,888  | 7,818,182,656   |

| 16GB     | 0x1D5C000 | 30,785,536  | 15,762,194,432  |

| 32 GB    | 0x3A40000 | 61,079,552  | 31,272,730,624  |

| 64 GB    | 0x7480000 | 122,159,104 | 62,545,461,248  |

Note: 1 sector = 512 bytes.

The total usable capacity of the e-NAND may be less than total physical capacity becuase a small portion of the capacity is used for NAND flash management and maintenance purpose.

#### ■ Maximum Enhanced Partition Size

Enhanced User Data Area can be configured to store read-centric data such as sensitive data or for other host usage models. SK hynix e-NAND support Enhanced User Data Area as SLC Mode. When customer adopts some portion as enhance user data area in User Data Area, that area occupies double the size of the original set-up size. Enhanced User Data Area of e-NAND guarantees 20K program and erase cycles

| Capacity | Max ENH_SIZE_MULTI | HC_ERASE_GRP_SIZE | HC_WP_GRP_SIZE |

|----------|--------------------|-------------------|----------------|

| 8GB      | 1D2h               | 1h                | 10h            |

| 16GB     | 3ABh               | 1h                | 10h            |

| 32 GB    | 748h               | 1h                | 10h            |

| 64 GB    | 748h               | 1h                | 20h            |

Note: 1 sector = 512 bytes.

Max Enhanced Partition Size is defined as MAX\_ENH\_SIZE\_MULT x HC\_WP\_GRP\_SIZE x HC\_ERASE\_GRP\_SIZE x 512Byte. (refer to Table 32. Extended CSD)

| Capacity | LBA(Hex) | LBA(Dec) | Capacity(Bytes) |

|----------|----------|----------|-----------------|

| 8GB      | 1D2h     | 7,456    | 3,817,472       |

| 16GB     | 3AB0h    | 15,024   | 7,692,288       |

| 32 GB    | 7480h    | 29,824   | 15,269,888      |

| 64 GB    | E900h    | 59,648   | 30,539,776      |

#### 5.3 Write Endurance

This section provide "TBW(Total Bytes Written) refer to how much total data can be written to an e-NAND for a given workload before the device reaches its endurance limits."

The data is based on the SK hynix's data pattern, which is designed to be a good indication of endurance for mainstream application users.

Table 3: Write Endurance.

| Density | TBW   |

|---------|-------|

| 8GB     | TBD   |

| 16GB    | 6.2TB |

| 32GB    | 22TB  |

| 64GB    | TBD   |

#### 5.4 Boot Operation

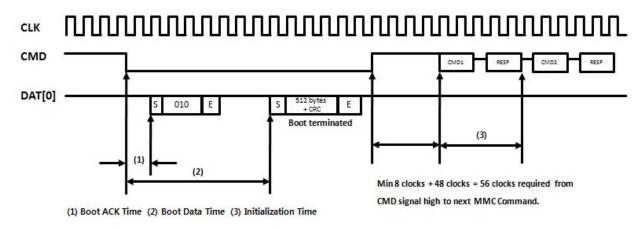

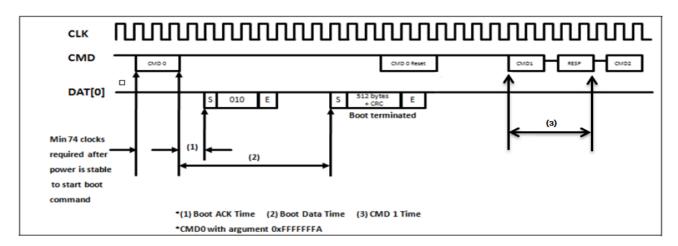

e-NAND supports Boot Mode and Alternative Boot Mode. e-NAND also, supports high speed timing and dual data rate during boot.

Figure 10: e-NAND state diagram (Boot Mode)

Figure 11: e-NAND state diagram (Alternative Boot Mode)

| Timing Factor           | Value   |

|-------------------------|---------|

| (1) Boot ACK Time       | < 50 ms |

| (2) Boot Data Time      | < 1 sec |

| (3) Initialization Time | < 1 sec |

<sup>1)</sup> Initialization time includes partition setting, Please refer to INI\_TIMEOUT\_AP in 7.4 Extended CSD Register. Initialization time is completed within 1sec from issuning CMD1 until receving Respons.

<sup>2)</sup> The device has to send the acknowledge pattern "010" to the master within 50ms after the CMD0 with the argument of 0xFFFFFFA is received.

<sup>3)</sup> Boot ACK Time can be over 50ms in worst case.

#### 5.5 Power Modes

#### 5.5.1 e-NAND power-up guidelines

e-NAND power-up must adhere to the following guidelines:

- When power-up is initiated, either VCC or VCCQ can be ramped up first, or both can be ramped up simultaneously.

- After power up, e-NAND enters the pre-idle state. The power up time of each supply voltage should be less than the specified tPRU (tPRUH, tPRUL or tPRUV) for the appropriate voltage range.

- If e-NAND does not support boot mode or its BOOT\_PARTITION\_ENABLE bit is cleared, e-NAND moves immediately to the idle state. While in the idle state, e-NAND ignores all bus transactions until receiving CMD1. e-NAND begins boot operation with the argument of 0xFFFFFFA. If a boot acknowledge is finished, e-NAND shall send acknowledge pattern "010" to the host within the specified time. After boot operation is terminated, e-NAND enters the idle state and shall be ready for CMD1 operation. If e-NAND receives CMD1 in the pre-boot state, it begins to respond to the command and moves to the card identification mode.

- When e-NAND is initiated by alternative boot command(CMD0 with arg=0xFFFFFFA), all the data will be read from the boot partition and then e-NAND automatically goes to idle state. But hosts are still required to issue CMD0 with arg=0x0000000000 in order to complete a boot mode properly and move to the idle state. While in the idle state, e-NAND ignores all bus transactions until it receives CMD1.

- CMD1 is a special synchronization command which is used to negotiate the operating voltage range and poll the device until it is out of its power-up sequence. In addition to the operating voltage profile of the device, the response to CMD1 contains a busy flag indicating that the device is still working on its power-up procedure and is not ready for identification. This bit informs the host that the device is not ready, and the host must wait until this bit is cleared. The device must complete its initialization within 1 second of the first CMD1 issued with a valid OCR range.

- If the e-NAND device was successfully partitioned during the previous power up session (bit 0 of EXT\_CSD byte [155] PARTITION\_SETTING\_COMPLETE successfully set) then the initialization delay is (instead of 1s) calculated from INI\_TIMEOUT\_PA (EXT\_CSD byte [241]). This timeout applies only for the very first initialization after successful paritioning. For all the consecutive initialization 1sec time out will be applied.

- The bus master moves the device out of the idle state. Because the power-up time and the supply ramp-up time depend on the application parameters such as the bus length and the power supply unit, the host must ensure that power is built up to the operating level (the same level that will be specified in CMD1) before CMD1 is transmitted.

- After power-up, the host starts the clock and sends the initializing sequence on the CMD line. The sequence length is the longest of: 1ms, 74 clocks, the supply ramp-up time, or the boot operation period. An additional 10 clocks (beyond the 64 clocks of the power-up sequence) are provided to eliminate power-up synchronization problems.

- Every bus master must implement CMD1.

#### 5.5.2 e-NAND Power Cycling

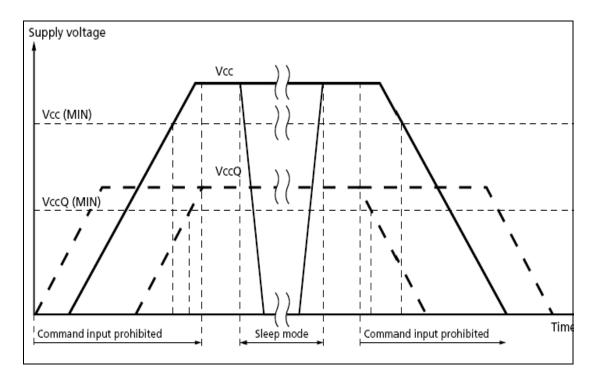

The master can execute any sequence of VCC and VCCQ power-up/power-down. However, the master must not issue any commands until VCC and VCCQ are stable within each operating voltage range. After the slave enters sleep mode, the master can power-down VCC to reduce power consumption. It is necessary for the slave to be ramped up to VCC before the host issues CMD5 (SLEEP\_AWAKE) to wake the slave unit.

Figure 12: e-NAND power cycle

If VCC or VCCQ are below 0.5 V for longer than 1 ms, the slave shall always return to the pre-idle state, and perform the appropriate boot behavior. The slave will behaves as in a standard power up condition once the voltages have returned to their functional ranges.

An exception to the this behavior is if the device is in sleep state, in which the voltage on VCC is not monitored.

### 5.5.3 Leakage

**Table 4: General operation conditions**

| Parameter                                                                                             |     | Symbol | Min  | Max.     | Unit | Remark |  |  |

|-------------------------------------------------------------------------------------------------------|-----|--------|------|----------|------|--------|--|--|

|                                                                                                       | BGA |        | -0.5 | VccQ+0.5 | V    |        |  |  |

| All inputs                                                                                            |     |        |      |          |      |        |  |  |

| Input leakage current (before initialization sequenceand/or the internalpull up resistors connected)  |     |        | -100 | 100      | μΑ   |        |  |  |

| Input leakage current (after initialization sequence and the internal pull up resistors disconnected) |     |        | -2   | 2        | μΑ   |        |  |  |

| All outputs                                                                                           |     |        |      |          |      |        |  |  |

| Output leakage current (before initialization sequence)                                               |     |        | -100 | 100      | μΑ   |        |  |  |

| Output leakage current (after initialization sequence)                                                |     |        | -2   | 2        | μΑ   |        |  |  |

• NOTE 1. Initialization sequence is defined in JEDEC Section 10.1 on page 178

### 5.5.4 Power Supply

In e-NAND, VCC is used for the NAND core voltage and NAND interface; VCCQ is for the controller core and e-NAND interface voltage shown in **Figure 13**. The core regulator is optional and only required when internal core logic voltage is regulated from VCCQ. A Creg capacitor must be connected to the VDDi terminal to stabilize regulator output on the system.

VCC -VCCQ Control Signals Core Regulator RESET-Block NAND I/O Block (Required for 3.3V VCCQ) Memory VDDi -MMC I/O Data Strobe Core Data Bus Logic CMD Block DAT[7:0] MMC Controller

Figure 13: e-NAND internal power diagram

e-NAND supports one or more combinations of VCC and VCCQ as shown in **Table 5**. The available voltage configuration is shown in **Table 6**.

Table 5: e-NAND power supply voltage

| Parameter                | Symbol | Min  | Max. | Unit | Remark        |   |

|--------------------------|--------|------|------|------|---------------|---|

| Supply voltage (NAND)    | VCC    | 2.7  | 3.6  | V    |               |   |

| Supply Voltage (IVAIVD)  | VCC    | 1.7  | 1.95 | V    | Not supported |   |

| Supply voltage (I/O)     | VCCQ . | 2.7  | 3.6  | V    |               |   |

| Supply voltage (1/0)     |        | vccQ | VCCQ | 1.7  | 1.95          | V |

| Supply power-up for 3.3V | tPRUH  |      | 35   | ms   |               |   |

| Supply power-up for 3.3V | tPRUL  |      | 25   | ms   |               |   |

| Supply power-up for 3.3V | tPRUV  |      | 20   | ms   |               |   |

Table 6: e-NAND voltage combinations

|     |            | VCCQ         |             |  |

|-----|------------|--------------|-------------|--|

|     |            | 1.7V ~ 1.95V | 2.7V ~ 3.6V |  |

| vcc | 2.7V-3.6V  | Valid        | Valid       |  |

| VCC | 1.7V-1.95V | NOT VALID    | NOT VALID   |  |

# **5.5.5 Active Power Consumption during operation**

| Density   | Max RMS current |                                                |  |  |

|-----------|-----------------|------------------------------------------------|--|--|

|           | Icc             | Iccq                                           |  |  |

| 32GB(QDP) | TBD             | 180mA<br>(HS200 Mode)<br>200mA<br>(HS400 Mode) |  |  |

**Table 7: e-NAND Active Power Consumption during operation**

Note 1 : Room temperature\_25  $^{\circ}$ C

Note 2 : RMS current consumption is over a period of 20ms

# 5.5.6 Low Power Mode

# • Standby Power Mode

|         |           | NA          | ND          | CTRL        |             |  |

|---------|-----------|-------------|-------------|-------------|-------------|--|

| Density |           | <b>25</b> ℃ | <b>85</b> ℃ | <b>25</b> ℃ | <b>85</b> ℃ |  |

|         | 32GB(QDP) | TBD         | TBD         | TBD         | TBD         |  |

Note 1: In Standby Power mode, CTRL Vccq & NAND Vcc power supply is swuched on.

# • Sleep Power Mode

|           | NA          | ND  | CTRL        |             |  |

|-----------|-------------|-----|-------------|-------------|--|

| Density   | <b>25</b> ℃ | 85℃ | <b>25</b> ℃ | <b>85</b> ℃ |  |

| 32GB(QDP) | 0           | 0   | TBD         | TBD         |  |

Note 1: In sleep state, triggered by CMD5, NAND Vcc power supply is swuched off (CTRL Vccq on)

# **5.6 Erase Write Protect Group Size**

| / |                       |                  |                  |                  |                  |                  |  |  |  |

|---|-----------------------|------------------|------------------|------------------|------------------|------------------|--|--|--|

|   |                       | Write<br>Block 0 | Write<br>Block 1 | Write<br>Block 2 | Write<br>Block 3 | Write<br>Block n |  |  |  |

|   | Erase Group 0         |                  |                  |                  |                  |                  |  |  |  |

|   | [                     | Erase Group      | 1                |                  |                  |                  |  |  |  |

|   | [                     | Erase Group      | 2                |                  |                  |                  |  |  |  |

|   |                       | Erase Group      | 3                |                  |                  |                  |  |  |  |

|   | [ [                   | Erase Group      | n                |                  |                  |                  |  |  |  |

|   | (N                    | Vrite Protect G  | Group 0          |                  |                  |                  |  |  |  |

|   | $\overline{}$         |                  |                  |                  |                  |                  |  |  |  |

|   | Write Protect Group 1 |                  |                  |                  |                  |                  |  |  |  |

|   | Write Protect Group 2 |                  |                  |                  |                  |                  |  |  |  |

|   | Write Protect Group 3 |                  |                  |                  |                  |                  |  |  |  |

|   |                       |                  |                  |                  |                  |                  |  |  |  |

|       | Erase gro         | Write protect group size |                          |

|-------|-------------------|--------------------------|--------------------------|

|       | ERASE_GROUP_DEF=0 | ERASE_GROUP_DEF=1        | Write protect group size |

| 8GB   | 512KB             | 512KB                    | 8MB                      |

| 16GB  | 512KB             | 512KB                    | 8MB                      |

| 32 GB | 512KB             | 512KB                    | 8MB                      |

| 64 GB | 512KB             | 512KB                    | 16MB                     |

# 5.7 Timings

# **5.7.1 Time Out**

| Timing parameter                          | Value                                         | Remark                                               |

|-------------------------------------------|-----------------------------------------------|------------------------------------------------------|

| Read Timeout                              | Max 100 ms                                    |                                                      |

| Write Timeout<br>(CMD to Write Done)      | Max 500ms                                     |                                                      |

| Write Timeout<br>(Data to Data)           | Max 300ms                                     |                                                      |

| Erase Timeout                             | Max 300 ms                                    |                                                      |

| Force erase Timeout                       | Max 3 min                                     |                                                      |

| Trim Timeout                              | Max 300ms                                     |                                                      |

| Secure Trim 1                             | Max 300ms                                     | Only marking write block                             |

| Secure Trim 2                             | Max 300ms<br>(Max 15 Min to Erase Physically) | Perform a secure purge operation                     |

| Secure Erase                              | Max 300ms<br>(Max 15 Min to Erase Physically) | Map data invalid only                                |

| Discard                                   | Max 300ms                                     |                                                      |

| Partition switch Time                     | Max 1ms                                       | Measured time after initialization                   |

| Initialization Timeout                    | Max 500ms                                     | CMD to Response                                      |

| PON Busy Time (Short / Long)              | Max 50ms / 1000ms                             | PON Long busy time includes Garbage collection time. |

| PON Initialization Time<br>(Short / Long) | Max 180ms                                     |                                                      |

| BKOP Exit Time                            | Max 20ms                                      | BKOP Off time after HPI                              |

| Auto-BKOP Exit Time                       | Max 100ms                                     | BKOP Off time after any CMD from Host                |

| HPI                                       | Max 100ms                                     | Response after HPI                                   |

| Auto-standby Time-out                     | Max 50ms                                      |                                                      |

| Auto-suspend Timeout                      | Max 40us                                      | Fast wake up from Auto suspend at idle state         |

| CMD5 Sleep In                             | 3ms                                           |                                                      |

| Sliding Window                            | Max 256ms                                     |                                                      |

-. NAND I/F: DDR 200Mhz, 16KB page size.

-. eMMC I/F: HS400, x16

-. Pre-conditioning states - Clean state / Test Range: Random Write - 1GB, Random Read - 1GB

-. Sequential Read / Write chunk size: 1MB

-. Current numbers are based on aligned 4KB

-. Maximum 4-way interleaving

### 5.7.2 Bus Timing

<sup>t</sup>PP tWH -- min (V<sub>IH</sub>) tWL 50% V<sub>DD</sub> CLK 50%  $V_{DD}$ --- max (V<sub>IL</sub>) THL TLH  $min \; (V_{IH})$ Data Invalid Data Input max (V<sub>IL</sub>) tOH, <sup>t</sup>ODLY tosu --- min (V<sub>OH</sub>) Data Data Output Invalid - max (VoL)

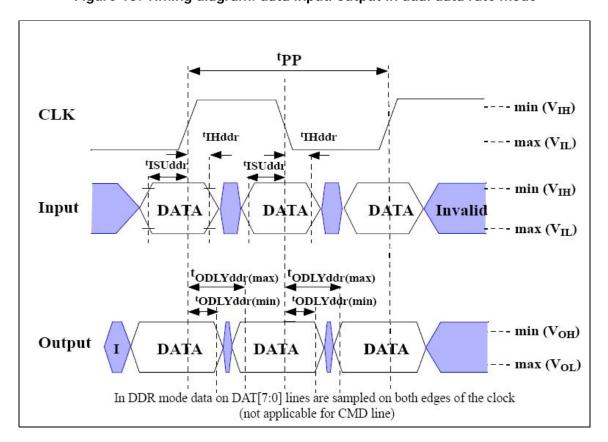

Figure 14: Timing diagram: data input/output

Data must always be sampled on the rising edge of the clock.

Table 8: High-speed e-NAND interface timing

| Parameter                                              | Symbol          | Min | Max               | Unit | Remark                                      |  |  |

|--------------------------------------------------------|-----------------|-----|-------------------|------|---------------------------------------------|--|--|

| Clock CLK <sup>(1)</sup>                               |                 |     |                   |      |                                             |  |  |

| Clock frequency Data Transfer Mode (PP) <sup>(2)</sup> | f <sub>PP</sub> | 0   | 52 <sup>(3)</sup> | MHz  | C <sub>L</sub> ≤30 pF<br>Tolerance: +100KHz |  |  |

| Clock frequency Identification Mode (OD)               | fOD             | 0   | 400               | kHz  | Tolerance: +20KHz                           |  |  |

| Clock high time                                        | tWH             | 6.5 |                   | ns   | $C_L \le 30 \text{ pF}$                     |  |  |

| Clock low time                                         | tWL             | 6.5 |                   | ns   | C <sub>L</sub> ≤ 30 pF                      |  |  |

| Clock rise time <sup>(4)</sup>                         | tTLH            |     | 3                 | ns   | C <sub>L</sub> ≤ 30 pF                      |  |  |

| Clock fall time                                        | tTHL            |     | 3                 | ns   | C <sub>L</sub> ≤ 30 pF                      |  |  |

| Inputs CMD, DAT (referenced to CLK)                    |                 |     |                   |      |                                             |  |  |

| Input set-up time                                      | tISU            | 3   |                   | ns   | C <sub>L</sub> ≤ 30 pF                      |  |  |

| Input hold time                                        | tIH             | 3   |                   | ns   | $C_L \le 30 \text{ pF}$                     |  |  |

| Outputs CMD, DAT (referenced to CLK)                   |                 |     |                   |      |                                             |  |  |

| Output delay time during data transfer                 | tODLY           |     | 13.7              | ns   | C <sub>L</sub> ≤ 30 pF                      |  |  |

| Output hold time                                       | tOH             | 2.5 |                   | ns   | $C_L \le 30 \text{ pF}$                     |  |  |

| Signal rise time <sup>(5)</sup>                        | tRISE           |     | 3                 | ns   | $C_L \le 30 \text{ pF}$                     |  |  |

| Signal fall time                                       | tFALL           |     | 3                 | ns   | C <sub>L</sub> ≤ 30 pF                      |  |  |

- NOTE 1. CLK timing is measured at 50% of VDD.

- NOTE 2. e-NAND shall support the full frequency range from 0-26Mhz, or 0-52MHz

- NOTE 3. Card can operate as high-speed card interface timing at 26 MHz clock frequency.

- NOTE 4. CLK rising and falling times are measured by min (VIH) and max (VIL).

- NOTE 5. Inputs CMD, DAT rise and fall times are measured by min (VIH) and max (VIL), and outputs CMD, DAT rise and fall times are measured by min (VOH) and max (VOL).

Table 9: Backward-compatible e-NAND interface timing

| Parameter                                              | Symbol           | Min  | Max | Unit | Remark <sup>(1)</sup> |  |  |

|--------------------------------------------------------|------------------|------|-----|------|-----------------------|--|--|

| Clock CLK <sup>(2)</sup>                               |                  |      |     |      |                       |  |  |

| Clock frequency Data Transfer Mode (PP) <sup>(3)</sup> | fPP              | 0    | 26  | MHz  | CL ≤ 30 pF            |  |  |

| Clock frequency Identification Mode (OD)               | fOD              | 0    | 400 | kHz  |                       |  |  |

| Clock high time                                        | tWH              | 10   |     | ns   | CL ≤ 30 pF            |  |  |

| Clock low time                                         | tWL              | 10   |     | ns   | CL ≤ 30 pF            |  |  |

| Clock rise time <sup>(4)</sup>                         | tTLH             |      | 10  | ns   | CL ≤ 30 pF            |  |  |

| Clock fall time                                        | t <sub>THL</sub> |      | 10  | ns   | CL ≤ 30 pF            |  |  |

| Inputs CMD, DAT (referenced to CLK)                    |                  |      |     |      |                       |  |  |

| Input set-up time                                      | tISU             | 3    |     | ns   | CL ≤ 30 pF            |  |  |

| Input hold time                                        | tIH              | 3    |     | ns   | CL ≤ 30 pF            |  |  |

| Outputs CMD, DAT (referenced to CLK)                   |                  |      |     |      |                       |  |  |

| Output set-up time <sup>(5)</sup>                      | tOSU             | 11.7 |     | ns   | CL ≤ 30 pF            |  |  |

| Output hold time <sup>(5)</sup>                        | tOH              | 8.3  |     | ns   | CL ≤ 30 pF            |  |  |

- NOTE 1. e-NAND must always start with the backward-compatible interface timing. The timing mode can be switched to high-speed timing by the host sending the SWITCH command (CMD6) with the argument for high speed interface select.

- NOTE 2. CLK timing is measured at 50% of VDD.

- NOTE 3. For compatibility with cards that support the v4.2 standard or earlier, host should not use > 20 MHz before switching to high-speed interface timing.

- NOTE 4. CLK rising and falling times are measured by min (VIH) and max (VIL).

- NOTE 5. tOSU and tOH are defined as values from clock rising edge. However, there may be cards or devices which utilize clock falling edge to output data in backward compatibility mode.

Therefore, it is recommended for hosts either to set tWL value as long as possible within the range which will not go over tCK-tOH(min) in the system or to use slow clock frequency, so that host could have data set up margin for those devices.

In this case, each device which utilizes clock falling edge might show the correlation either between tWL and tOSU or between tCK and tOSU for the device in its own datasheet as a note or its' application notes.

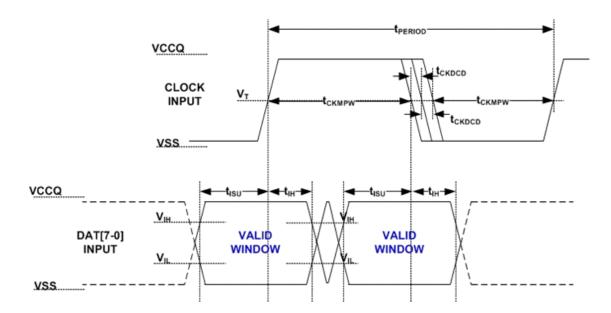

### 5.7.3 Bus Timing for DAT Signals During 2x Data Rate Operation

These timings apply to the DAT[7:0] signals only when the device is configured for dual data mode operation. In dual data mode, the DAT signals operate synchronously of both the rising and the falling edges of CLK. The CMD signal still operate synchronously with both the rising and falling edge of CLK and therefore complies with the bus timing specified in eMMC JEDEC spec. section 10.5, therefore there is no timing change for the CMD signal.

Figure 15: Timing diagram: data input/output in dual data rate mode

Table 10: Dual data rate interface timings

| Parameter                                | Symbol           | Min. | Max. | Unit | Remark                       |  |  |

|------------------------------------------|------------------|------|------|------|------------------------------|--|--|

| Input CLK <sup>(1)</sup>                 |                  |      | •    |      |                              |  |  |

| Clock duty cycle                         |                  | 45   | 55   | %    | Includes jitter, phase noise |  |  |

| Clock rise time                          | t <sub>TLH</sub> |      | 3    | ns   | CL≤30 pf                     |  |  |

| Clock fail time                          | t <sub>THL</sub> |      | 3    | ns   | CL≤30 pf                     |  |  |

| Input CMD (referenced to CLK-SDR mode    | e)               |      |      |      |                              |  |  |

| Input set-up time                        | tISUddr          |      |      | ns   | CL≤20 pf                     |  |  |

| Input hold time                          | tIHDDR           |      |      | ns   | CL≤20 pf                     |  |  |

| Output CMD (referenced to CLK-SDR mo     | de)              |      |      |      |                              |  |  |

| Output delay time during data transfer   | tODLY            |      | 13.7 | ns   | CL≤20 pf                     |  |  |

| Output hold time                         | tOH              | 2.5  |      | ns   | CL≤20 pf                     |  |  |

| Signal rise time                         | tRISE            |      | 3    | ns   | CL≤20 pf                     |  |  |

| Signal fall time                         | tFALL            |      | 3    | ns   | CL≤20 pf                     |  |  |

| Input DAT (referenced to CLK-DDR mode    | <del>)</del>     |      |      |      |                              |  |  |

| Input set-up time                        | tISUddr          | 2.5  |      | ns   | CL≤20 pf                     |  |  |

| Input hold time                          | tIHddr           | 2.5  |      | ns   | CL≤20 pf                     |  |  |

| Outputs DAT (referenced to CLK-DDR mode) |                  |      |      |      |                              |  |  |

| Output delay time during data transfer   | tODLYddr         | 1.5  | 7    | ns   | CL≤20 pf                     |  |  |

| Signal rise time(DAT0-7) <sup>(2)</sup>  | tRISE            |      | 2    | ns   | CL≤20 pf                     |  |  |

| Signal fall time (DAT0-7)                | tFALL            |      | 2    | ns   | CL≤20 pf                     |  |  |

<sup>•</sup> NOTE 1. CLK timing is measured at 50% of VDD.

<sup>•</sup> NOTE 2. Inputs DAT rise and fall times are measured by min (VIH) and max (VIL), and outputs CMD, DAT rise and fall times are measured by min (VOH) and max (VOL)

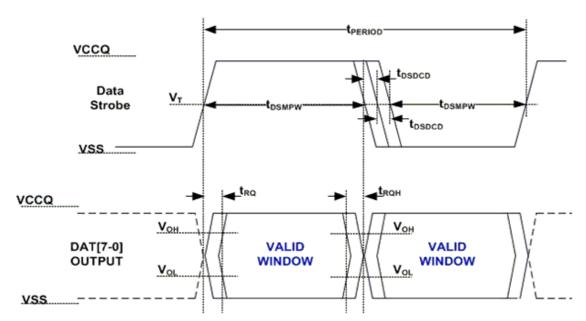

### 5.7.4 Bus Timing Specification in HS 400 Mode

**HS400 Device Input Timing**The CMD input timing for HS400 mode is the same as CMD input timing for HS 200 mode. (Previous bus timing parameter form DDR52 and HS200 mode are defined by JEDEC standard)

Figure 16. HS400 Device input timing

| Parameter                     | Symbol  | Min   | Max | Unit | Remark                                                                                                          |  |  |  |

|-------------------------------|---------|-------|-----|------|-----------------------------------------------------------------------------------------------------------------|--|--|--|

| Input CLK                     |         |       |     |      |                                                                                                                 |  |  |  |

| Cycle time data transfer mode | tPERIOD | 5     |     |      | 200MHz(Max), between rising edges with respect to $\mathrm{V}_{\mathrm{T}}$                                     |  |  |  |

| Slew rate                     | SR      | 1.125 |     | V/ns | With respect to V <sub>IH</sub> /V <sub>IL</sub>                                                                |  |  |  |

| Duty cycle<br>distortion      | tCKDCD  | 0.0   | 0.4 | ns   | Allowable deviation from an ideal 50% duty cycle. With respect to $V_{\text{T}}$ . Includes jitter, phase noise |  |  |  |

| Minimum pulse width           | tCKMPW  | 2.2   |     | ns   | With respect to V <sub>T</sub>                                                                                  |  |  |  |

| Input DAT (referenced to CLK) |         |       |     |      |                                                                                                                 |  |  |  |

| Input set-up time             | tISUddr | 0.4   |     | ns   | $C_{DEVICE} \le 6pF$<br>With respect to $V_{IH}/V_{IL}$                                                         |  |  |  |

| Input hold time               | tIHddr  | 0.4   |     | ns   | $C_{DEVICE} \le 6pF$<br>With respect to $V_{IH}/V_{IL}$                                                         |  |  |  |

| Slew rate                     | SR      | 1.125 |     | V/ns | With respect to $V_{IH}/V_{IL}$                                                                                 |  |  |  |

Table 12. HS400 Device input timing

# 5.7.4 Bus Timing Specification in HS 400 Mode

### **HS400 Device Output Timing**

The Data Stobe is used to read data in HS400 mode. The Data Strobe is toggled only during data read or CRC status response.

Figure 17. HS400 Device output timing

| Parameter                      | Symbol              | Min   | Max                       | Unit | Remark                                                                                                                  |

|--------------------------------|---------------------|-------|---------------------------|------|-------------------------------------------------------------------------------------------------------------------------|

| Data Strobe                    |                     |       |                           |      |                                                                                                                         |

| Cycle time data transfer mode  | t <sub>PERIOD</sub> | 5     |                           |      | 200MHz(Max), between rising edges with respect to $V_{\text{T}}$                                                        |

| Slew rate                      | SR                  | 1.125 |                           | V/ns | With respect to V <sub>IH</sub> /V <sub>IL and HS400</sub> reference load                                               |

| Duty cycle distortion          | tDSDCD              | 0.0   | 0.2                       | ns   | Allowable deviation from the input CLK duty cycle distortion(tCKDCD) With respect to $V_T$ Includes jitter, phase noise |

| Minimum pulse width            | tDSMPW              | 2.0   |                           | ns   | With respect to V <sub>T</sub>                                                                                          |

| Read pre-amble                 | t <sub>RPRE</sub>   | 0.4   | 5 (One Clock<br>Cycle)    | ns   |                                                                                                                         |

| Read post-amble                | t <sub>RPST</sub>   | 0.4   | 2.5 (Half Clock<br>Cycle) | ns   |                                                                                                                         |

| Output DAT (referenced to Data | a Strobe)           |       | •                         |      | -                                                                                                                       |

| Input set-up time              | tISUddr             |       |                           | ns   | $C_{DEVICE} \le 6pF$<br>With respect to $V_{IH}/V_{IL}$                                                                 |

| Output Skew                    | tRQ                 |       | 0.4                       | ns   | With respect to V <sub>OH</sub> /V <sub>OL</sub> and HS400 reference load                                               |

| Output hold skew               | tRQH                |       | 0.4                       | ns   | With respect to V <sub>OH</sub> /V <sub>OL</sub> and HS400 reference load                                               |

| Slew rate                      | SR                  | 1.125 |                           | V/ns | With respect to V <sub>OH</sub> /V <sub>OL</sub> and HS400 reference load                                               |

Table 12. HS400 Device Output timing

# Table 13. HS400 Capacitance

| Parameter                                | Symbol              | Min | Туре | Max | Unit | Remark |

|------------------------------------------|---------------------|-----|------|-----|------|--------|

| Pull-up resistance for CMD               | R <sub>CMD</sub>    | 4.7 |      | 100 | Kohm |        |

| Pull-up resistance for DAT0-7            | R <sub>DAT</sub>    | 10  |      | 100 | Kohm |        |

| Pull-down resistance for Data strobe     | R <sub>DS</sub>     | 10  |      | 100 | Kohm |        |

| Internal pull up resistance<br>DAT1-DAT7 | R <sub>int</sub>    | 10  |      | 150 | Kohm |        |

| Bus signal line capacitance              | CL                  |     |      | 13  | pF   |        |

| Single Device capacitance                | C <sub>Device</sub> |     |      | 6   | pF   |        |

# 5.8 Bus Signal

### 5.8.1 Bus Signal Line Load

The total capacitance  $C_L$  of each line of e-MMC bus is the sum of the bus master capacitance  $C_{HOST}$ , the bus capacitance  $C_{BUS}$  itself, and the capacitance  $C_{Device}$  of the eMMC connected to this line, and requiring the sum of the host and bus capacitances not to exceed 20 pF (see Table 14).

$$C_L = C_{HOST} + C_{BUS} + C_{Device}$$

Table 14: e-NAND Capacitance

| Parameter                                  | Symbol                          | Min | Тур | Max | Unit | Remark                                                                                                                                 |

|--------------------------------------------|---------------------------------|-----|-----|-----|------|----------------------------------------------------------------------------------------------------------------------------------------|

| Pull-up resistance for CMD                 | R <sub>CMD</sub>                | 4.7 |     | 100 | Kohm | to prevent bus floating                                                                                                                |

| Pull-up resistance for DAT0-7              | R <sub>DAT</sub>                | 10  |     | 100 | Kohm | to prevent bus floating                                                                                                                |

| Internal pull up resistance<br>DAT1 - DAT7 | R <sub>int</sub>                | 10  |     | 150 | Kohm |                                                                                                                                        |

| Bus signal line capacitance                | C <sub>L</sub>                  |     |     | 30  | pF   | Single Device                                                                                                                          |

| Single e-NAND capacitance                  | C <sub>DEVICE</sub>             |     |     | 12  | pF   |                                                                                                                                        |

| Maximum signal line inductance             |                                 |     |     | 16  | nH   | f <sub>PP</sub> ≤ 52 MHz                                                                                                               |

| VDDi capacitor value                       | C <sub>REG</sub> <sup>(2)</sup> | 0.1 |     |     | uF   | To stablize regulator output when targt device bus speed mode is either backward-compatible, high speed SDR, high speed DDR, or HS200. |

|                                            |                                 | 1   |     |     | uF   | To stablize regulator output when target device bus speed mode is HS400                                                                |

| VCCQ decoupling capacitor                  | C <sub>H1</sub>                 | 1   |     |     | uF   | (3), (4), (5)                                                                                                                          |

<sup>(1)</sup> Recommended maximum pull-up is 30 Kohm for 1.2 V and 50Kohm for 1.8V interface supply voltages. A 3V part, may use the whole range up to 100Kohms.

<sup>(2)</sup> Recommended value for C<sub>REG</sub> might be different between *e*-MMC device vendors. Please confirm the maximum value and the accuracy of the capacitance with *e*-MMC vendor because the electrical characteristics of the regulator inside *e*-MMC is affected by the fluctuation of the capacitance.

<sup>(3)</sup> CH1 is VccQ-VssQ decoupling capacitor required for HS200&HS400 eMMC device.

<sup>(4)</sup> CH1 should be placed adjacent to VccQ-VssQ balls (#K6 and #K4 accordingly, next to DAT[7..0] balls). It should be located as close as possible to the balls defined in order to minimize connection parasitics.

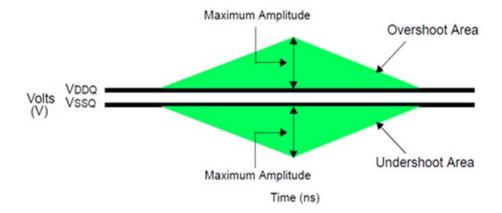

# 5.8.2 Overshoot / Undershoot Specification

|                                                     |     | V <sub>CCQ</sub> | Unit  |

|-----------------------------------------------------|-----|------------------|-------|

|                                                     |     | 1.70V - 1.95V    | Oilit |

| Maximum peak amplitude allowed for overshoot area.  | Max | 0.9              | V     |

| Maximum peak amplitude allowed for undershoot area. | Max | 0.9              | V     |

| Maximum area above V <sub>CCQ</sub>                 | Max | 1.5              | V-ns  |

| Maximum area below V <sub>SSQ</sub>                 | Max | 1.5              | V-ns  |

Figure 18. Overshoot / Undershoot definition

# 5.8.2 Bus Signal Levels

As the bus can be supplied with a variable supply voltage, all signal levels are related to the supply voltage.

Input

High Level

VoH

VoH

VoH

Undefined

VoL

Low Level

Vss

t

Figure 19: e-NAND bus signal level

# • Open-Drain mode bus signal level

Table 15: Open-Drain signal level

| Parameter           | Symbol          | Min.                  | Max. | Unit | Conditions            |

|---------------------|-----------------|-----------------------|------|------|-----------------------|

| Output HIGH voltage | V <sub>OH</sub> | V <sub>DD</sub> - 0.2 |      | V    | Note <sup>1)</sup>    |

| Output LOW voltage  | V <sub>OL</sub> |                       | 0.3  | V    | I <sub>OL</sub> = 2mA |

(1) Because Voh depends on external resistance value (including outside the package), this value does not apply as device specifiaction. Host is responsible to choose the external pull-up and open drain resistance value to meet Voh Min Value.

# • Push-Pull mode bus signal level

The device input and output voltages shall be within the following specified ranges for any VDD of the allowed

Table 16: Push-Pull signal level 2.7V-3.6V VCCQ range

| Parameter           | Symbol          | Min.                    | Max.                     | Unit | Conditions                                      |

|---------------------|-----------------|-------------------------|--------------------------|------|-------------------------------------------------|

| Output HIGH voltage | V <sub>OH</sub> | 0.75 * V <sub>DD</sub>  |                          | V    | I <sub>OH</sub> = -100μA @ V <sub>CCQ</sub> min |

| Output LOW voltage  | V <sub>OL</sub> |                         | 0.125 * V <sub>CCQ</sub> | V    | $I_{OL}$ = -100 $\mu$ A @ $V_{CCQ}$ min         |

| Input HIGH voltage  | V <sub>IH</sub> | 0.625 * V <sub>DD</sub> | V <sub>CCQ</sub> + 0.3   | V    |                                                 |

| Input LOW voltage   | V <sub>IL</sub> | V <sub>SS</sub> - 0.3   | 0.25 * V <sub>CCQ</sub>  | V    |                                                 |

Table 17: Push-pull signal level 1.65V-1.95V VCCQ range

| Parameter           | Symbol          | Min.                   | Max.                   | Unit | Conditions |

|---------------------|-----------------|------------------------|------------------------|------|------------|

| Output HIGH voltage | V <sub>OH</sub> | VDD - 0.45V            |                        | V    | IOH = -2mA |

| Output LOW voltage  | V <sub>OL</sub> |                        | 0.45V                  | V    | IOL = -2mA |

| Input HIGH voltage  | V <sub>IH</sub> | 0.65 * V <sub>DD</sub> | V <sub>DD</sub> + 0.3  | V    |            |

| Input LOW voltage   | V <sub>IL</sub> | V <sub>SS</sub> - 0.3  | 0.35 * V <sub>DD</sub> | V    |            |

- Note:

1) 0.7\*VCCQ for eMMC 4.3 and older revisions.

2) 0.3\*VCCQ for eMMC 4.3 and older revisions.

### 5.9 Performance

Performance measured using IOZone test with EXT4 file system.

| Data transfer unit | 512KB    | 1024KB   |

|--------------------|----------|----------|

| Sequential Read    | 170 MB/s | 200 MB/s |

| Sequential Write   | 80 MB/s  | 80 MB/s  |

| Data transfer unit | 4KB      | 8КВ      |

| Random Read        | 4K IOPS  | 4K IOPS  |

| Random Write       | 3K IOPS  | 3K IOPS  |

- Note 1 : IOZone for Android based mobile platform.

- Note 2: Sequential performance measured using IOZone test with 512KB & 1024KB of data transfer unit size.

- Note 3: Random performance measured using IOZone test with 4KB & 8KB of data transfer unit size.

- Note 4 : Speed may vary due to host hardware, software and usage.

- Density: 32GB QDP

- 200MHz DDR, Cache operation

# 6. Commands

### **6.1 Command Classes**

The command set of e-NAND is divided into several classes. Each class supports a subset of e-NAND functions.

The supported e-NAND command Classes are coded as a parameter in the eMMC specific data (CSD) register, providing the host with information on how to access the e-NAND.

Table 18: Supported eMMC command classes

| e-NAND           | Class                |   |   |   |   |   |   |   |   |   |   | Sup | por | t con | nmar | ıds |    |    |    |    |    |    |    |    |    |

|------------------|----------------------|---|---|---|---|---|---|---|---|---|---|-----|-----|-------|------|-----|----|----|----|----|----|----|----|----|----|

| command<br>class | description          | 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10  | 11  | 12    | 13   | 14  | 15 | 16 | 17 | 18 | 19 | 20 | 23 | 24 | 25 |

| Class 0          | basic                | + | + | + | + | + | + | + | + | + | + | +   |     | +     | +    | +   | +  |    |    |    | +  |    |    |    |    |

| Class 1          | obsolete             |   |   |   |   |   |   |   |   |   |   |     |     |       |      |     |    |    |    |    |    |    |    |    |    |

| Class 2          | block read           |   |   |   |   |   |   |   |   |   |   |     |     |       |      |     |    | +  | +  | +  |    |    | +  |    |    |

| Class 3          | obsolete             |   |   |   |   |   |   |   |   |   |   |     |     |       |      |     |    |    |    |    |    |    |    |    |    |

| Class 4          | block write          |   |   |   |   |   |   |   |   |   |   |     |     |       |      |     |    | +  |    |    |    |    | +  | +  | +  |

| Class 5          | erase                |   |   |   |   |   |   |   |   |   |   |     |     |       |      |     |    |    |    |    |    |    |    |    |    |

| Class 6          | write protection     |   |   |   |   |   |   |   |   |   |   |     |     |       |      |     |    |    |    |    |    |    |    |    |    |

| Class 7          | lock eMMC            |   |   |   |   |   |   |   |   |   |   |     |     |       |      |     |    | +  |    |    |    |    |    |    |    |

| Class 8          | Application specific |   |   |   |   |   |   |   |   |   |   |     |     |       |      |     |    |    |    |    |    |    |    |    |    |

| Class 9          | I/O mode             |   |   |   |   |   |   |   |   |   |   |     |     |       |      |     |    |    |    |    |    |    |    |    |    |

| Class 10         | Security mode        |   |   |   |   |   |   |   |   |   |   |     |     |       |      |     |    |    |    |    |    |    |    |    |    |

| Class 11         | reserved             |   |   |   |   |   |   |   |   |   |   |     |     |       |      |     |    |    |    |    |    |    |    |    |    |

| e-NAND           | Class                 |    | Support commands |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

|------------------|-----------------------|----|------------------|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|

| command<br>class | description           | 26 | 27               | 28 | 29 | 30 | 31 | 35 | 36 | 38 | 39 | 40 | 42 | 42 | 49 | 53 | 54 | 55 | 56 |

| Class 0          | basic                 |    |                  |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

| Class 1          | stream read           |    |                  |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

| Class 2          | block read            |    |                  |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

| Class 3          | stream write          |    |                  |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

| Class 4          | block write           | +  | +                |    |    |    |    |    |    |    |    |    |    | +  | +  |    |    |    |    |

| Class 5          | erase                 |    |                  |    |    |    |    | +  | +  | +  |    |    |    |    |    |    |    |    |    |

| Class 6          | write<br>protection   |    |                  | +  | +  | +  | +  |    |    |    |    |    |    |    |    |    |    |    |    |

| Class 7          | lock eMMC             |    |                  |    |    |    |    |    |    |    |    |    | +  |    |    |    |    |    |    |

| Class 8          | Application specific  |    |                  |    |    |    |    |    |    |    |    |    |    |    |    |    |    | +  |    |

| Class 9          | I/O mode              |    |                  |    |    |    |    |    |    |    | +  | +  |    |    |    |    |    |    |    |

| Class10          | Security<br>Protocols |    |                  |    |    |    |    |    |    |    |    |    |    |    |    | +  | +  |    |    |

| Class11          | reserved              |    |                  |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

### 6.2 Command

The following tables define in detail all e-NAND commands.

Table 19: Basic command (class 0 and class 1)

| CMD   | Туре    | Argument            | Resp               | Abbreviation         | Command description                                         |

|-------|---------|---------------------|--------------------|----------------------|-------------------------------------------------------------|

| INDEX | . , , , | J                   |                    | 7.001011011          | ·                                                           |

| CMD0  | bc      | [31:0] 00000000     | -                  | GO IDLE STATE        | Resets e-NAND to idle state                                 |

|       | bc      | [31:0] F0F0F0F0     | -                  | GO PRE IDLE STATE    | Resets e-NAND to pre-idle state                             |

|       | -       | [31:0] FFFFFFA      | -                  | BOOT INITIATION      | Inititiate alternative boot operation                       |

| CMD1  | bcr     | [31:0] OCR with-out | R3                 | SEND_OP_COND         | Asks e-NAND, in idle state, to send its Operating Condi-    |

|       |         | busy                |                    |                      | tions Register contents in the response on the CMD line.    |

| CMD2  | bcr     | [31:0] stuff bits   | R2                 | ALL_SEND_CID         | Asks e-NAND to send its CID number on the CMD line          |

| CMD3  | ac      | [31:16] RCA         | R1                 | SET_RELATIVE_ADDR    | Assigns relative address to e-NAND                          |

|       |         | [15:0] stuff bits   |                    |                      |                                                             |

| CMD4  | bc      | [31:16] DSR         | -                  | SET_DSR              | Programs the DSR of e-NAND                                  |

|       |         | [15:0] stuff bits   |                    |                      |                                                             |

| CMD5  | ac      | [31:16] RCA         | R1b                | SLEEP_AWAKE          | Toggles the card between Sleep state and Standby            |

|       |         | [15] Sleep/Awake    |                    |                      | state.                                                      |

|       |         | [14:0] stuff bits   |                    |                      |                                                             |

| CMD6  | ac      | [31:26] Set to 0    | R1b                | SWITCH               | Switches the mode of operation of e-NAND the                |

|       |         | [25:24] Access      |                    |                      | EXT_CSD registers.                                          |

|       |         | [23:16] Index       |                    |                      |                                                             |

|       |         | [15:8] Value        |                    |                      |                                                             |

|       |         | [7:3] Set to 0      |                    |                      |                                                             |

|       |         | [2:0] Cmd Set       |                    |                      |                                                             |

| CMD7  | ac      | [31:16] RCA         | R1/                | SELECT/DESELECT_CARD | Command toggles e-NAND between the stand-by and             |

|       |         | [15:0] stuff bits   | R1b <sup>(1)</sup> |                      | transfer states or between the programming and dis-         |

|       |         |                     |                    |                      | connect states. In both cases e-NAND is selected by its     |

|       |         |                     |                    |                      | own relative address and gets deselected by any other       |

|       |         |                     |                    |                      | address; address 0 deselects e-NAND.                        |

| CMD8  | adtc    | [31:0] stuff bits   | R1                 | SEND_EXT_CSD         | e-NAND sends its EXT_CSD register as a block of data.       |

| CMD9  | ac      | [31:16] RCA         | R2                 | SEND_CSD             | e-NAND sends its card-specific data (CSD) on the CMD        |

|       |         | [15:0] stuff bits   |                    |                      | line.                                                       |

| CMD10 | ac      | [31:16] RCA         | R2                 | SEND_CID             | e-NAND sends its card identification (CID) on CMD the       |

|       |         | [15:0] stuff bits   |                    |                      | line.                                                       |

| CMD11 |         |                     |                    | obsolete             | The response to CMD11 will be undefined.                    |

| CMD12 | ac      | [31:16]RCA3         | R1/                | STOP_TRANSMISSION    | Forces e-NAND to stop transmission. If HPI flag is set      |

|       |         | [15:1]stuff bits    | R1b4               |                      | the device shall interrupt itsinternal operations in a well |

|       |         | [0]HPI              |                    |                      | defined timing.                                             |

Table 19: Basic commands and read-stream command (class 0 and class 1) (continued)

| CMD<br>INDEX | Туре | Argument                                    | Resp | Abbreviation      | Command description                                                                                                                         |

|--------------|------|---------------------------------------------|------|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------|

| CMD13        | ac   | [31:16] RCA<br>[15:1] stuff bits<br>[0] HPI | R1   | SEND_STATUS       | Addressed Device sends its status register. If HPI flag is set the device shall innterrupt its internal operations in a well defined timing |

| CMD14        | adtc | [31:0] stuff bits                           | R1   | BUSTEST_R         | A host reads the reversed bus testing data pattern from e-NAND.                                                                             |

| CMD15        | ac   | [31:16] RCA<br>[15:0] stuff bits            | -    | GO_INACTIVE_STATE | Sets e-NAND to inactive state                                                                                                               |

| CMD19        | adtc | [31:0] stuff bits                           | R1   | BUSTEST_W         | A host sends the bus test data pattern to e-NAND.                                                                                           |

<sup>•</sup> NOTE 1. R1 while selecting from Stand-By State to Transfer State; R1b while selecting from Disconnected State to Programming State.

NOTE 2. RCA in CMD12 is used only if HPI bit is set. The argument does not imply any RCA check on the device side.

NOTE 3. R1 for read cases and R1b for write cases.

Table 20: Block-oriented read commands (class 2)

| CMD<br>INDEX | Туре | Argument                           | Resp | Abbreviation            | Command description                                                                                                                                     |

|--------------|------|------------------------------------|------|-------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| CMD16        | ac   | [31:0] block length                | R1   | SET_BLOCKLEN            | Sets the block length (in bytes) for all following block commands (read and write). Default block length is specified in the CSD.                       |

| CMD17        | adtc | [31:0] data address <sup>(1)</sup> | R1   | READ_SINGLE_BLOCK       | Reads a block of the size selected by the<br>SET_BLOCKLEN command.2                                                                                     |

| CMD18        | adtc | [31:0] data address <sup>(1)</sup> | R1   | READ_MULTIPLE_<br>BLOCK | Continuously transfers data blocks from e-NAND to<br>host until interrupted by a stop command, or the<br>requested number of data blocks is transmitted |

| CMD21        | adtc | [31:0] stuff bits                  | R1   | SEND_TUNING_<br>BLOCK   | 128 clocks of tuning pattern(64byte in 4bit mode or 128byte in 8 bit mode)is sent for HS200 optimal sampling point detection                            |

NOTE 1. Data address for media =<2GB is a 32bit byte address and data address for media > 2GB is a 32bit sector (512B) address.

NOTE 2. The transferred data must not cross a physical block boundary, unless READ\_BLK\_MISALIGN is set in the CSD register.

Table 21: Stream write commands (class 3)

| CMD<br>INDEX | Туре     | Argument | Resp | Abbreviation | Command Description                      |

|--------------|----------|----------|------|--------------|------------------------------------------|

| CMD20        |          |          |      | Obsolete     | The response to CMD20 will be undefined. |

| CMD22        | reserved |          |      |              |                                          |