## V390416VAT 4M Bit Parallel STT-MRAM

**Preliminary**

The V390416VAT chip utilizes advanced pMTJ STT-MRAM technology and is a non-volatile MRAM device with an ASRAM interface. This device provides a parallel bus, offers read and write cycles up to 35ns, and boasts excellent reliability with over 10 years of data retention. The chip also features low-voltage write protection to prevent accidental data writes.

The V39C304161VAT35 chip offers the following key features:

- Capacity

- · 4Mbit

- Asynchronous interface supporting 16/8-bit data addressing

- · Read and write cycles up to 35ns

- · 16-bit I/O with support for UBN/LBN switching

- Operating Voltage

- · Standard voltage: Single VDD 3.3V

- •Operating Temperature

- $\cdot$  -40°C to 125°C

- Data Protection

- · Data write protection is enabled when the voltage drops below 2.5V (typical)

- Power Consumption

- · Static Power Consumption 1.7mA (typical)

- · Dynamic Power Consumption Read Operation 20mA (typical)

- · Dynamic Power Consumption Write Operation 35mA (typical)

1

- Reliability

- · Maximum Erase/Write Endurance 1E12

- · Retention ≥10 years @ 125°C

- Package

- · 44-Pin TSOP II

# Table of Content

| 1. Product Overview          | •••••           | 1               |

|------------------------------|-----------------|-----------------|

| 2. Logic Block Diagram       |                 | 3               |

| 3. Package Information       |                 | 3               |

| 4. Pin Description           |                 | 4               |

| 5. Operating Mode            |                 | 4               |

| 6. Power-On/Power-Off C      | haracteristics  | 5               |

| 7. Chip Functions            |                 | 5               |

| 7.1 AC Char                  | acteristics Tes | st Conditions 5 |

| 7.2 Write Mo                 | ode             | 6               |

| 7.3 Read Mo                  | de              | 11              |

| 8. Absolute Operating Cor    | nditions        |                 |

| 9. Electrical Characteristic | es              |                 |

| 9.1 Operating                | g Conditions    |                 |

| 9.2 Pin Capa                 | citance         |                 |

| 9.3 DC Char                  | acteristics     |                 |

| 10. Precautions for Use      |                 |                 |

| 11. Package Outline          |                 |                 |

| 12. Product Naming Rules     |                 |                 |

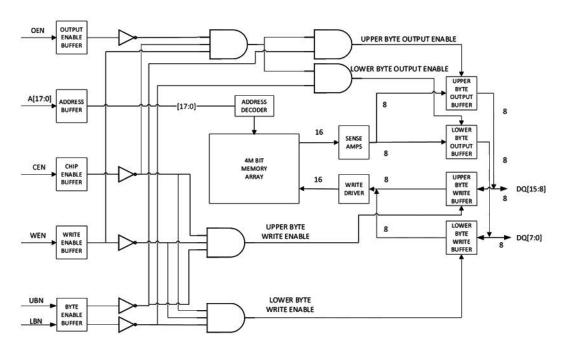

## 2. Logic Block Diagram

This chip implements an asynchronous data interface through five control signals: CEN, WEN, UBN, LBN, and OEN. The chip's logic block diagram is shown in Figure 1.

Figure 1 Chip block diagram

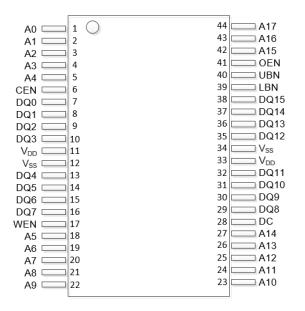

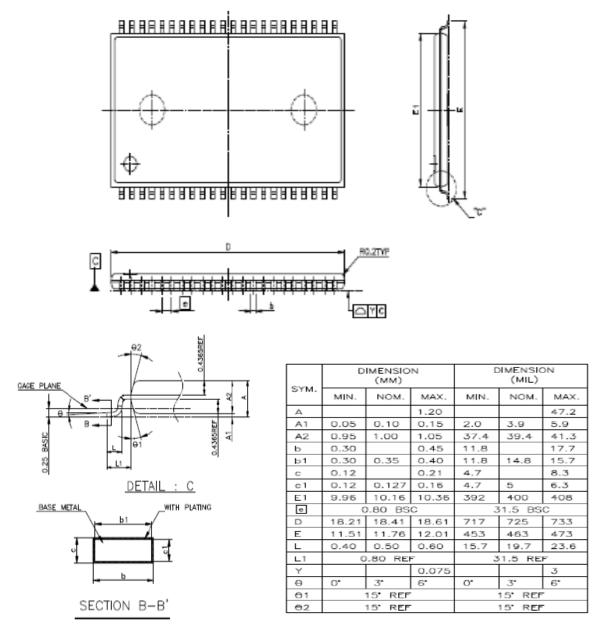

## 3. Packaging Information

Figure 2 44-Pin TSOP II

# 4. Pin Descriptions

| Interface | Interface Type | Interface Description                 |

|-----------|----------------|---------------------------------------|

| A         | Input          | Input Address Bit                     |

| CEN       | Input          | Chip Select Signal, Active Low        |

| WEN       | Input          | Write Enable Signal, Active Low       |

| OEN       | Input          | Output Data Enable Signal, Active Low |

| UBN       | Input          | High BYTE Enable Signal, Active Low   |

| LBN       | Input          | Low BYTE Enable Signal, Active Low    |

| DQ        | Input / Output | Parallel Data Input/Output Pin        |

| VDD       | -              | Power Supply                          |

| Vss       | -              | Ground                                |

Table 1 Pin Descriptions

# 5. Operation Modes

| CEN | OEN | WEN | UBN | LBN | Mode            | VDD current | DQ[7:0] | DQ[15:8] |

|-----|-----|-----|-----|-----|-----------------|-------------|---------|----------|

| Н   | X   | X   | X   | X   | Unselected      | ISB1        | Hi-Z    | Hi-Z     |

| L   | Н   | Н   | X   | X   | Output Disable  | Iddr        | Hi-Z    | Hi-Z     |

| L   | X   | X   | Н   | Н   | Output Disable  | Iddr        | Hi-Z    | Hi-Z     |

| L   | L   | Н   | L   | Н   | Low Byte read   | Iddr        | Dout    | Hi-Z     |

| L   | L   | Н   | Н   | L   | High Byte read  | Iddr        | Hi-Z    | Dout     |

| L   | L   | Н   | L   | L   | 16-bit read     | Iddr        | Dout    | Dout     |

| L   | X   | L   | L   | Н   | Low Byte write  | IDDW        | Din     | Hi-Z     |

| L   | X   | L   | Н   | L   | High Byte write | IDDW        | Hi-Z    | Din      |

| L   | X   | L   | L   | L   | 16-bit Write    | IDDW        | Din     | Din      |

Notes:

Table 2 Operation Modes

1. H = 1, L = 0, X = Don't Care state

2. Hi-Z = High Impedance state

## 6. Power-on/Power-off Characteristics

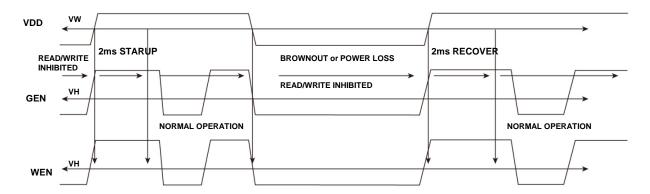

When VDD is less than VWI, the chip enters a write-protected state, preventing users from successfully writing data. After VDD exceeds VDD(min), a 2ms power-up time (power stabilization time) is required before read and write operations can be performed. During power-up, the CEN and WEN signals should rise to VDD-0.2V or VIH (whichever is lower) along with VDD and remain high during the power-up time. In most systems, the CEN and WEN pins can be pulled up with resistors to ensure they remain high even when the drive signals are in a high-impedance state at power-up. The CEN and WEN pins should remain high during a power-on reset and for a duration longer than the power-up time. If VDD drops below VWI due to power failure or voltage fluctuations, write operations are prohibited. When power is restored and VDD exceeds VDD(min), the power-up time must be waited for.

Figure 3 Power-on and Power-off timing diagram

## 7. Chip Functions

#### 7.1 AC Characteristics Test Conditions

| Parameter                                          | Value                                                     | Unit |  |

|----------------------------------------------------|-----------------------------------------------------------|------|--|

| Reference level of Logic input timing measurement  | 1.5                                                       | V    |  |

| Reference level of Logic output timing measurement | 1.5                                                       | V    |  |

| Logic input pulse level                            | 0 or 3.0                                                  | V    |  |

| Input rise/fall time                               | 2                                                         | ns   |  |

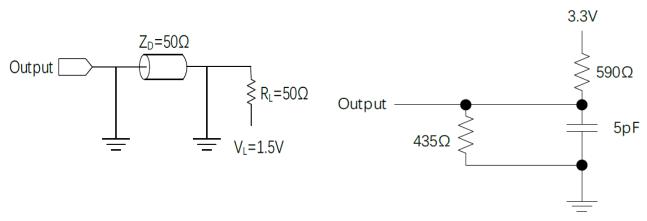

| Output load for Low-impedance and High-impedance   | See Figure 4                                              |      |  |

| Output load for all other timing parameters        | Output load for all other timing parameters  See Figure 5 |      |  |

Table 3 AC characteristic test conditions

Figure 4 Output load test (for low impedance and high impedance parameters)

Figure 5 Output load test (for all others)

## 7.2 Write Mode

| Symbol         | Parameter                                      | Min. | Max. | Unit |

|----------------|------------------------------------------------|------|------|------|

| tavav          | Write cycle time (*2)                          | 35   | -    | ns   |

| tavwl          | Address creation time                          | 0    | -    | ns   |

| tavwh          | Address valid until write completes (OEN high) | 18   | -    | ns   |

| tavwh          | Address valid until write completes (OEN low)  | 20   | -    | ns   |

| twlwh<br>twleh | Write pulse width (OEN high)                   | 15   | -    | ns   |

| twlwh<br>twleh | Write pulse width (OEN low)                    | 15   | -    | ns   |

| <b>t</b> dvwh  | Data is valid until the write is completed     | 10   | -    | ns   |

| <b>t</b> whdx  | Data retention time                            | 0    | -    | ns   |

| twlqz          | WEN low to data Hi-Z (*3)                      | 0    | 12   | ns   |

| twнqх          | WEN high to output active (*3)                 | 3    | -    | ns   |

| twhax          | Write recovery time                            | 12   | -    | ns   |

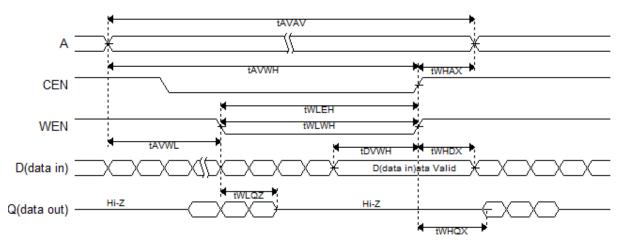

Table 4 Write cycle timing 1 (WEN control) (\*1)

- \*1. All write operations occur during the overlap between CEN low and WEN low. Power supplies must be properly grounded and decoupled, and bus contention must be reduced or eliminated during read and write cycles. If OEN is pulled low during a write cycle, to reduce bus contention, OEN must be pulled low at the same time WEN is low or begins to go low, at least 2ns before WEN is pulled high. Pulling OEN low during WEN high will increase power consumption due to bus contention. The minimum time between CEN low in one cycle and CEN low in the next cycle must be equal to the minimum cycle allowed by the chip.

- \*2. All write cycle times are calculated from the arrival of the last address bit to the transition time of the first address bit.

- \*3. This parameter is a sample test, not a 100% device test. Signal transitions are measured within a ±200 mV range of the steady-state voltage. At any given voltage or temperature, tWLQZ (max) < tWHQX (min). The V39C304161VAT35 chip utilizes advanced pMTJ STT-MRAM technology and is a non-volatile MRAM device with an ASRAM interface. This device provides a parallel bus, offers read and write cycles up to 35ns, and boasts excellent reliability with over 10 years of data retention. The chip also features low-voltage write protection to prevent accidental data writes.

Figure 6 Write cycle timing 1 (WEN control)

| Symbol         | Parameter                                      | Min. | Max. | Unit |

|----------------|------------------------------------------------|------|------|------|

| tavav          | Write cycle time (*2)                          | 35   | -    | ns   |

| tavel          | Address creation time                          | 0    | -    | ns   |

| taveh          | Address valid until write completes (OEN high) | 18   | -    | ns   |

| taveh          | Address valid until write completes (OEN low)  | 20   | -    | ns   |

| teleh<br>telwh | Write pulse width (OEN high)                   | 15   | -    | ns   |

| teleh<br>telwh | Write pulse width (OEN low) (*3)               | 15   | -    | ns   |

| tdveh          | Data is valid until the write is completed     | 10   | -    | ns   |

| tehdx          | Data retention time                            | 0    | -    | ns   |

| tehax          | Write recovery time                            | 12   | -    | ns   |

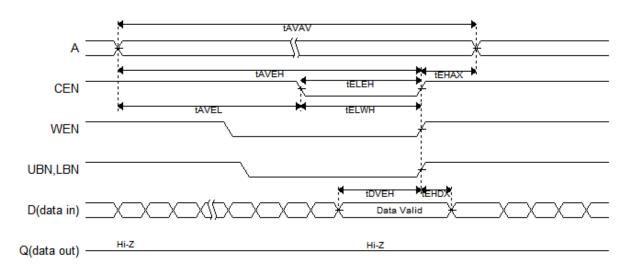

Table 5 Write cycle timing 2 (CEN control) \*1

- \*1. All write operations occur during the overlap between CEN low and WEN low. Power supplies must be properly grounded and decoupled, and bus contention must be reduced or eliminated during read and write cycles. If OEN is pulled low during a write cycle, to reduce bus contention, OEN must be pulled low at the same time WEN goes low or begins to go low, at least 2ns before WEN goes high. Pulling OEN low during WEN high will increase power consumption due to bus contention. The minimum time between CEN low in one cycle and CEN low in the next cycle must be equal to the minimum cycle time allowed by the chip.

- \*2. All write cycle times are calculated from the arrival of the last address bit to the transition time of the first address bit.

- \*3. If CEN goes low at the same time as WEN goes low or begins to go low, the outputs will remain in a high-impedance state. If CEN goes high before or at the same time as WEN goes high, the outputs will remain in a high-impedance state.

Figure / Write cycle timing 2 (CEN control)

| Symbol         | Parameter                                      | Min. | Max. | Unit |

|----------------|------------------------------------------------|------|------|------|

| tavav          | Write cycle time (*2)                          | 35   | -    | ns   |

| tavbl          | Address creation time                          | 0    | -    | ns   |

| tavbh          | Address valid until write completes (OEN high) | 18   | -    | ns   |

| tavbh          | Address valid until write completes (OEN low)  | 20   | -    | ns   |

| tbleh<br>tblwh | Write pulse width (OEN high)                   | 15   | -    | ns   |

| tbleh<br>tblwh | Write pulse width (OEN low)                    | 15   | -    | ns   |

| tdvbh          | Data is valid until the write is completed     | 10   | -    | ns   |

| tBHDX          | Data retention time                            | 0    | -    | ns   |

| tbhax          | Write recovery time                            | 12   | -    | ns   |

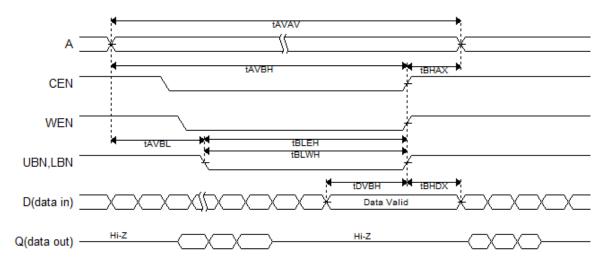

Table 6 Write cycle timing 3 (LBN/UBN control) (\*1)

#### Note:

\*1. All write operations must occur during the overlap between CEN low and WEN low. Power supplies must be properly grounded and decoupled, and bus contention must be reduced or eliminated during read and write cycles. If OEN is pulled low during a write cycle, to reduce bus contention, OEN must be pulled low at the same time WEN is low or begins to go low, at least 2ns before WEN goes high. Pulling OEN low during WEN high will increase power consumption due to bus contention. When both UBN and LBN are active, ensure that the skew between the two signals is less than 2ns. The minimum time between CEN low in one cycle and CEN low in the next cycle must be equal to the minimum cycle allowed by the chip.

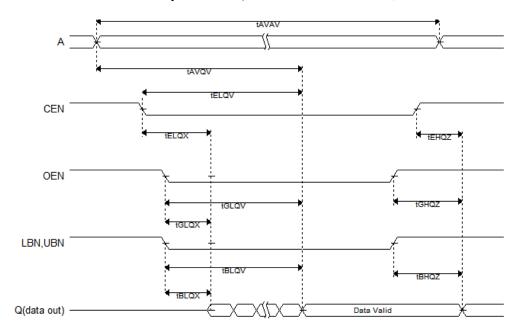

Figure 8 Write cycle timing 3 (LBN/UBN control)

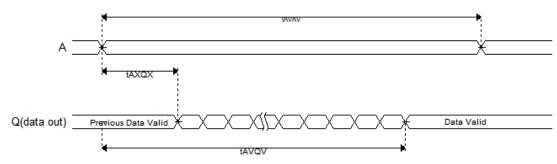

#### 7.3 Read Mode

| Symbol | Parameter                                    | Min. | Max. | Unit |

|--------|----------------------------------------------|------|------|------|

| tavav  | Read cycle time                              | 35   | -    | ns   |

| tavqv  | Address access time                          | -    | 35   | ns   |

| telqv  | Enable access time (*2)                      | -    | 35   | ns   |

| tGLQV  | Output enable access time                    | -    | 15   | ns   |

| tBLQV  | Byte enable access time                      | -    | 15   | ns   |

| taxqx  | Output hold after address change             | 3    | -    | ns   |

| telqx  | Enable low level to output active (*3)       | 3    | -    | ns   |

| tGLQV  | Output enable low to output active           | 0    | -    | ns   |

| tBLQX  | Byte enable low to output active             | 0    | -    | ns   |

| tehqz  | Enable high level to output Hi-Z (*3)        | 0    | 15   | ns   |

| tGHQZ  | Output enable high level to output Hi-Z (*3) | 0    | 10   | ns   |

| tвнqz  | Byte high level to output Hi-Z*3             | 0    | 10   | ns   |

Table 7 Read cycle timing (\*1)

<sup>\*1.</sup> During a read cycle, WEN must be high. Power supplies must be properly grounded and decoupled, and bus contention must be reduced or eliminated during read and write cycles.

<sup>\*2.</sup> The address is valid before CEN is low or goes low.

<sup>\*3.</sup> This parameter is a sample test and not a 100% device test. Signal transitions are measured within a  $\pm 200$  mV range based on steady-state voltage.

Figure 9 Read cycle timing 1

Note: The device is continuously selected (CEN  $\leq$  V1L, OEN  $\leq$  V1L)

Figure 10 Read cycle timing 2

## 8. Absolute Operating Conditions

| Symbol          | Parameter                                             | Value                         | Unit |

|-----------------|-------------------------------------------------------|-------------------------------|------|

| V <sub>DD</sub> | Supply voltage (*1)                                   | -0.5 to 4.0                   | V    |

| Vin             | Any pin voltage (*1)                                  | -0.5 to V <sub>DD</sub> + 0.5 | V    |

| Іоит            | Output current per pin                                | ±20                           | mA   |

| PD              | Package power consumption (*2)                        | 0.6                           | W    |

| TBIAS           | Bias temperature                                      | -40 to 125                    | °C   |

| Tstg            | Storage temperature                                   | -55 to 150                    | °C   |

| TLead           | Pin soldering temperature (up to 3 minutes)           | 260                           | °C   |

| Hmax_write      | Maximum magnetic field during writing (*3)            | 18000                         | A/m  |

| Hmax_read       | Maximum magnetic field during reading or standby (*3) | 50000                         | A/m  |

Table 8 Extreme working conditions

- \*2. Power consumption depends on package characteristics and operating environment.

- \*3. Maximum magnetic field values during write, read, and standby are measured with the magnetic field perpendicular to the chip surface and for 30 days. Chip magnetic resistance is closely related to magnetic field duration and direction. Please refer to the Magnetic Field Environment Application Guide for more detailed chip magnetic resistance information.

<sup>\*1.</sup> All voltages are referenced to Vss.

### 9. Electrical Characteristics

## 9.1. Working Conditions

| Symbol | Parameter             | Min. | Typical | Max. | Unit |

|--------|-----------------------|------|---------|------|------|

| Vdd    | Supply voltage (*1)   | 2.7  | 3.3     | 3.6  | V    |

| TA     | Temperature           | -40  | -       | 125  | °C   |

| VwT    | Write inhibit voltage | 2.4  | 2.5     | 2.7  | V    |

Table 9 Working conditions

Note:

# 9.2. Pin Capacitance

| Symbol | Parameter                 | Typical | Max. | Unit |

|--------|---------------------------|---------|------|------|

| CIna   | Address input capacitance | -       | 6    | pF   |

| CInc   | Control input capacitance | -       | 6    | pF   |

| CI/O   | Input/output capacitors   | -       | 8    | pF   |

Table 10 Pin capacitance

Note: f=1.0MHz, dV=3.0V, TA=25°C. Sampling test, not full test.

<sup>\*1.</sup> All voltages are referenced to Vss.

#### 9.3. DC Characteristics

| Symbol           | Parameter            | <b>Test condition</b>                                | Min.           | Typical | Max.                 | Unit |

|------------------|----------------------|------------------------------------------------------|----------------|---------|----------------------|------|

| T <sub>7-7</sub> | Input leakage        | Vin = 0                                              |                |         | ±1                   | μΑ   |

|                  | current              | Vin = VDD (max)                                      | -              | 1       | <u>-1</u>            |      |

| II. o            | Output leakage       | Vout = 0                                             |                |         | ±1                   | μΑ   |

| Ilo              | current              | $V_{out} = V_{DD (max)}$                             | _              | -       | <u> </u>             |      |

| Vih              | Input high level     | -                                                    | 2.2            | -       | V <sub>DD</sub> +0.3 | V    |

| VIL              | Input low level      | -                                                    | -0.5           | -       | 0.8                  | V    |

| Vон              | Output high<br>level | Iон = -4 mA<br>Iон = -100 uA                         | 2.4<br>Vdd-0.2 |         |                      | V    |

| Vol              | Output low level     | IOL = +4  mA $IOL = +100  uA$                        |                |         | 0.4<br>Vss+0.2       | V    |

| Iddr             | Read current (*1)    | $I_{OUT} = 0 \text{ mA}$ $V_{DD} = \max$             | -              | 20      | -                    | mA   |

| Iddw             | Write current (*2)   | $V_{DD} = max$                                       | -              | 35      | -                    | mA   |

| Isb1             | Standby current      | VDD = max , CEN = VDD , Other pins have fixed levels | -              | 1.7     | -                    | mA   |

Table 11 DC characteristics

<sup>\*1.</sup> Read power consumption is measured under the condition of the shortest read cycle 35ns.

<sup>\*2.</sup> Write power consumption is measured under the conditions of the shortest write cycle of 35ns and the shortest write pulse width of 15ns. As the proportion of write pulse width to write cycle increases, write power consumption will increase.

## 10. Precautions for Use

It is recommended that users program the chip after reflow soldering, because the chip cannot guarantee that the data written before reflow soldering will still be valid after reflow soldering.

## 11. Package Outline

Figure 11 Package outline

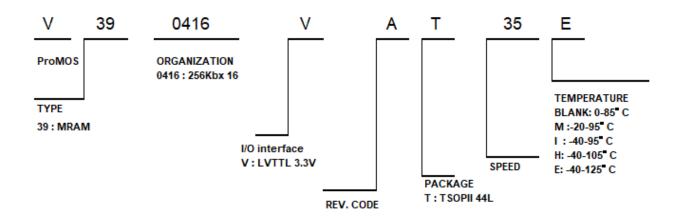

# 11. Product Naming Rules

Figure 12 Naming rules description