# **SK hynix e-NAND Product Family eMMC5.1 Compatible**

# **Revision History**

| Revision No. | History                                                                                                                                                                                                                                                                                                                    | Date          | Remark |

|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|--------|

| 1.0          | - 1 <sup>st</sup> Official release                                                                                                                                                                                                                                                                                         | May. 20, 2015 |        |

| 1.1          | - Change 'FFU argument' value in 'send FW to device' from 0x6600 to 0xFFFAFFF0 (p.19)                                                                                                                                                                                                                                      | May. 22, 2015 |        |

| 1.2          | - Add 'Vccq=2.7V ~ 3.6V' (p.4)<br>- Change 'The last value of PNM' from '1' to '2' (p.65)                                                                                                                                                                                                                                  | May. 28, 2015 |        |

| 1.3          | <ul> <li>Modify VENDOR_PROPRIETARY_HEALTH_REPORT[301-270] (p.22)</li> <li>Change the typo: bit[0] value of Cache Flush Policy (p.33)</li> <li>Modify 4.2.7 RPMB throughput improvement (p.43)</li> <li>Change 'PON Busy Time' (p.63)</li> <li>Modify CSD/EXT_CSD values of 64GB (WP_GRP_SIZE, etc.) (p.68 ~ 73)</li> </ul> | Jul. 07, 2015 |        |

# **Table of Contents**

| 1. Introduction                              | 4  |

|----------------------------------------------|----|

| 1.1 General Description                      |    |

| 1.2 Product Line-up                          |    |

| 1.3 Key Features                             |    |

|                                              |    |

| 2. Package Configurations                    | 5  |

| 2.1 Pin connection                           | 5  |

| 2.2 Package Mechanical Drawing               | 7  |

| 3. e-NAND Characteristics                    | •  |

|                                              |    |

| 3.1 Performance                              |    |

| 3.2 Power                                    | 10 |

| 4. e-NAND new features (eMMC5.0 and eMMC5.1) | 12 |

| 4.1 eMMC5.0 New features                     | 12 |

| 4.1.1 HS400 mode                             |    |

| 4.1.2 Field firmware update                  |    |

| 4.1.3 Health(Smart) report                   | 22 |

| 4.1.4 Production state awareness             |    |

| 4.1.5 Sleep notification                     | 25 |

| 4.1.6 Secure removal type                    | 26 |

| 4.2 eMMC5.1 New features                     |    |

| 4.2.1 Command queuing                        |    |

| 4.2.2 Cache barrier                          |    |

| 4.2.3 Cache Flushing report                  |    |

| 4.2.4 Background operation(BKOP) control     |    |

| 4.2.5 Secure Write Protection                |    |

| 4.2.6 Enhanced strobe                        |    |

| 4.2.7 RPMB throughput improvement            | 43 |

| 5. e-NAND general parameters                 | 44 |

| 5.1 Timing                                   |    |

| 5.2 Bus signal                               |    |

| 5.3 Power mode                               | 53 |

| 5.4 Connection guide                         | 57 |

| 6. e-NAND basic operations                   | EO |

|                                              |    |

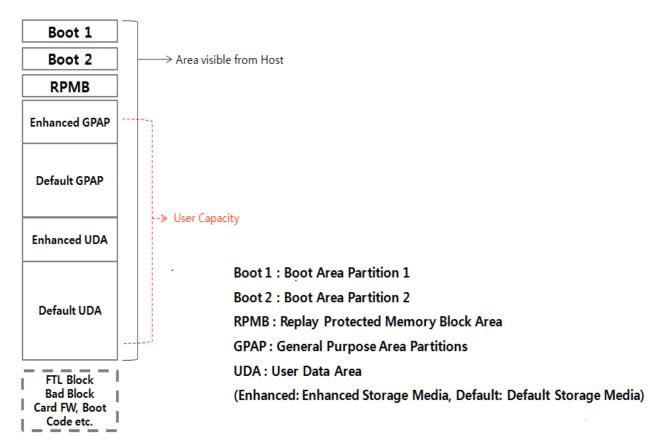

| 6.1 Partitioning                             |    |

| ·                                            |    |

| 7. Timeout                                   | 62 |

| 8. Register                                  | 64 |

| 8.1 Operation conditions register (OCR)      | 64 |

| 8.2 Card identification (CID) register       |    |

| 8.3 Card specific data register(CSD)         |    |

| 8.4 Extended CSD register                    |    |

| 8.5 RCA (Relative Card Address)              |    |

| 8.6 DSR (Driver Stage Register)              | 74 |

### 1. Introduction

# 1.1 General Description

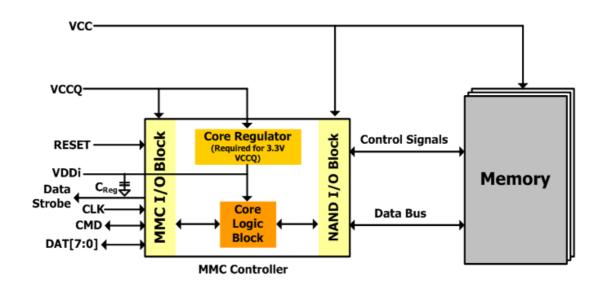

SK hynix e-NAND consists of NAND flash and MMC controller.

e-NAND has the built-in intelligent controller which manages interface protocols, wear leveling, bad block management, garbage collection, and ECC. e-NAND protects the data contents from the host sudden power off failure. e-NAND is compatible with JEDEC standard eMMC5.1 specification.

# 1.2 Product Line-up

| Density | Part Number  | NAND Stack | PKG Size (mm) | Package Type |

|---------|--------------|------------|---------------|--------------|

| 16GB    | H26M52208FPR | 64Gb x 2   | 11.5x13x0.8   |              |

| 32GB    | H26M64208EMR | 64Gb x 4   | 11.5x13x1.0   | 153FBGA      |

| 64GB    | H26M78208CMR | 64Gb x 8   | 11.5x13x1.0   |              |

#### 1.3 Key Features

# • eMMC5.1 compatible

(Backward compatible to eMMC4.5&eMMC5.0)

#### • Bus mode

Data bus width: 1bit(default), 4bits, 8bits

Data transfer rate: up to 400MB/s (HS400)

MMC I/F Clock frequency: 0~200MHz

MMC I/F Boot frequency: 0~52MHz

#### Operating Voltage Range

- V<sub>cc</sub> (NAND) : 2.7V - 3.6V

-  $V_{ccq}$  (Controller) : 1.7V - 1.95V / 2.7V  $\sim$  3.3V

#### Temperature

- Operation (-25° ~ +85°)

- Storage without operation (-40 $^{\circ}$  ~ +85 $^{\circ}$ )

#### Others

- This product is compliance with the RoHS directive

#### Supported Features

- HS400, HS200

- HPI, BKOPS, **BKOP operation control**

- Packed CMD, CMD queuing

- Cache, Cache barrier, Cache flushing report

- Partitioning, RPMB, RPMB throughput improve

- Discard, Trim, Erase, Sanitize

- Write protect, Secure write protection

- Lock/Unlock

- PON, Sleep/Awake

- Reliable Write

- Boot feature, Boot partition

- HW/SW Reset

- Field Firmware Update

- Configurable driver strength

- Health(Smart) report

- Production state awareness

- Secure removal type

- Data Strobe pin, Enhanced data strobe (Bold features are added in eMMC5.1)

# 2. Package Configurations

# 2.1 Pin connection

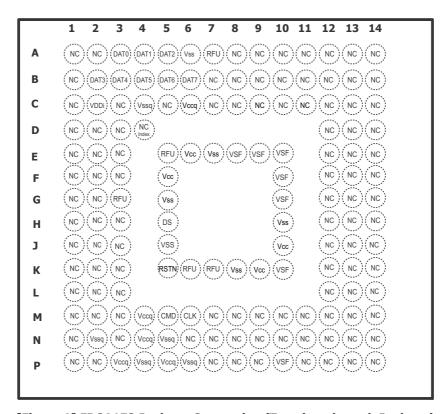

[Figure 1] FBGA153 Package Connection (Top view through Package)

| Pin number | Name     | Pin number | Name            | Pin number | Name            | Pin number | Name             |

|------------|----------|------------|-----------------|------------|-----------------|------------|------------------|

| А3         | DAT0     | C4         | $V_{ssq}$       | G10        | VSF             | M5         | CMD              |

| <b>A4</b>  | DAT1     | C6         | $V_{ccq}$       | Н5         | DS              | М6         | CLK              |

| <b>A</b> 5 | DAT2     | <b>E</b> 6 | V <sub>cc</sub> | H10        | V <sub>SS</sub> | N2         | V <sub>ssq</sub> |

| <b>A6</b>  | $V_{SS}$ | E7         | $V_{ss}$        | J5         | $V_{SS}$        | N4         | V <sub>ccq</sub> |

| В2         | DAT3     | E8         | VSF             | J10        | V <sub>cc</sub> | N5         | V <sub>ssq</sub> |

| В3         | DAT4     | <b>E</b> 9 | VSF             | К5         | RSTN            | Р3         | V <sub>ccq</sub> |

| В4         | DAT5     | E10        | VSF             | К8         | V <sub>SS</sub> | P4         | V <sub>ssq</sub> |

| В5         | DAT6     | F5         | V <sub>cc</sub> | К9         | V <sub>cc</sub> | P5         | V <sub>ccq</sub> |

| В6         | DAT7     | F10        | VSF             | K10        | VSF             | Р6         | $V_{ssq}$        |

| C2         | VDDi     | G5         | $V_{ss}$        | M4         | $V_{ccq}$       | P10        | VSF              |

| Name             | Туре    | Ball No.                        | Description                                                                                                                                                                                       |

|------------------|---------|---------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CLK              | Input   | M6                              | Clock: Each cycle directs a 1-bit transfer on the command and DAT lines.                                                                                                                          |

| CMD              | Input   | M5                              | Command: A bidirectional channel used for device initialization and command transfers. Command has two operating modes: 1) Open-drain for initialization. 2) Push-pull for fast command transfer. |

| DAT0             | I/O     | A3                              | Data I/O0: Bidirectional channel used for data transfer.                                                                                                                                          |

| DAT1             | I/O     | A4                              | Data I/O1: Bidirectional channel used for data transfer.                                                                                                                                          |

| DAT2             | I/O     | A5                              | Data I/O2: Bidirectional channel used for data transfer.                                                                                                                                          |

| DAT3             | I/O     | B2                              | Data I/O3: Bidirectional channel used for data transfer.                                                                                                                                          |

| DAT4             | I/O     | В3                              | Data I/O4: Bidirectional channel used for data transfer.                                                                                                                                          |

| DAT5             | I/O     | B4                              | Data I/O5: Bidirectional channel used for data transfer.                                                                                                                                          |

| DAT6             | I/O     | B5                              | Data I/O6: Bidirectional channel used for data transfer.                                                                                                                                          |

| DAT7             | I/O     | В6                              | Data I/O7: Bidirectional channel used for data transfer.                                                                                                                                          |

| RSTN             | Input   | K5                              | Reset signal pin                                                                                                                                                                                  |

| V <sub>cc</sub>  | Supply  | E6,F5,J10,K9                    | V <sub>cc</sub> : Flash memory I/F and Flash memory power supply.                                                                                                                                 |

| V <sub>ccq</sub> | Supply  | C6,M4,N4,P3,P5                  | V <sub>ccq</sub> : Memory controller core and MMC interface I/O power supply.                                                                                                                     |

| Vss              | Supply  | A6,E7,G5,H10,J5,K8              | V <sub>ss</sub> : Flash memory I/F and Flash memory ground connection.                                                                                                                            |

| Vssq             | Supply  | C4,N2,N5,P4,P6                  | V <sub>ssq</sub> : Memory controller core and MMC I/F ground connection                                                                                                                           |

| VDDi             |         | C2                              | VDDi: Connect 0.1uF capacitor from VDDi to ground.                                                                                                                                                |

| DS               | Out put | H5                              | DS: Data Strobe                                                                                                                                                                                   |

| VSF              | Supply  | E8,E9,E10,F10,<br>G10, K10, P10 | VSF: Vendor Specific Function<br>SK hynix use E9, E10 Pin as VSF Pin                                                                                                                              |

| RFU              |         |                                 | Reserved for future use                                                                                                                                                                           |

[Table 1] FBGA153 Ball Description

# 2.2 Package Mechanical Drawing

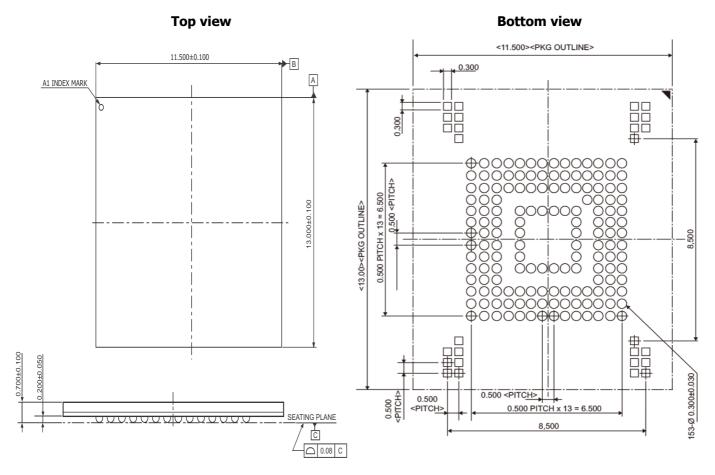

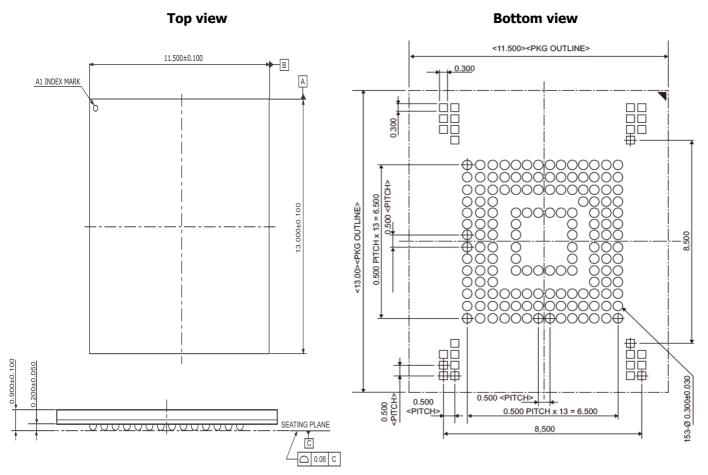

#### 2.2.1 11.5mm x13.0mm x0.8mm

[Figure 2] 11.5mm x 13.0mm x 0.8mm Package dimension

#### 2.2.2 11.5mm x13.0mm x1.0mm

[Figure 3] 11.5mm x13.0mm x 1.0mm Package dimension

# 3. e-NAND Characteristics

# 3.1 Performance

# • Packed CMD ON (Packed depth=8)

| Density       | Sequential Write<br>(MB/s) | Sequential Read<br>(MB/s) | Random Write<br>(IOPS) | Random Read<br>(IOPS) |

|---------------|----------------------------|---------------------------|------------------------|-----------------------|

| 16GB<br>(DDP) | 70                         | 280                       | 12K                    | 6.5K                  |

| 32GB<br>(QDP) | 140                        | 280                       | 15K                    | 6.5K                  |

| 64GB<br>(ODP) | 140                        | 280                       | 15K                    | 6.5K                  |

#### • Packed CMD OFF

| Density       | Sequential Write<br>(MB/s) | Sequential Read<br>(MB/s) | Random Write<br>(IOPS) | Random Read<br>(IOPS) |

|---------------|----------------------------|---------------------------|------------------------|-----------------------|

| 16GB<br>(DDP) | 70                         | 280                       | 8K                     | 5K                    |

| 32GB<br>(QDP) | 140                        | 280                       | 8K                     | 5K                    |

| 64GB<br>(ODP) | 140                        | 280                       | 8K                     | 5K                    |

• Tool : Device level • eMMC I/F speed : HS400

• Area : 1GB

Seq. chunk size: 512KBRan. chunk size: 4KBAdapted feature: Cache on

Status : SustainNot 100% tested

# 3.2 Power

# **3.2.1 Active Power Consumption During Operation**

| Den          | sity      | $\mathbf{I}_{cc}$ | I <sub>ccq</sub>           |

|--------------|-----------|-------------------|----------------------------|

| 16GB (DDP)   | Avg (mA)  | 100               | 130 (HS200)<br>140 (HS400) |

| 1000 (DDF)   | Peak (mA) | 200               | 200 (HS200)<br>230 (HS400) |

| 22(0, (000)) | Avg (mA)  | 180               | 130 (HS200)<br>140 (HS400) |

| 32GB (QDP)   | Peak (mA) | 300               | 200 (HS200)<br>230 (HS400) |

| 64GB (ODP)   | Avg (mA)  | 180               | 130 (HS200)<br>140 (HS400) |

|              | Peak (mA) | 300               | 200 (HS200)<br>230 (HS400) |

$\bullet$  Temperature : 25  $^\circ\! {\mathbb C}$

Average current consumption : over a period of 100ms

Peak current consumption : over a period of 20us

Vcc: 3.3VVccq: 1.8VNot 100% tested

# 3.2.2 Low Power Mode (Idle)

| Density    | Room Temperature (25℃) |                  | Hot Temper      | ature (85℃)      |

|------------|------------------------|------------------|-----------------|------------------|

| Delisity   | I <sub>cc</sub>        | I <sub>ccq</sub> | I <sub>cc</sub> | I <sub>ccq</sub> |

| 16GB (DDP) | Typ. 100uA             |                  | Max. 300uA      |                  |

| 32GB (QDP) | Typ. 200uA             | Typ. 150uA       | Max. 400uA      | Max. 650uA       |

| 64GB (ODP) | Typ. 400uA             |                  | Max. 500uA      |                  |

- $\bullet$  In Standby Power mode, CTRL  $V_{ccq}$  & NAND  $V_{cc}$  power supply is switched on

- No data transaction period before entering sleep status

- Not 100% tested.

# 3.2.3 Low Power Mode (CMD5 Sleep)

| Density    | Room Temperature (25℃) |                  | Hot Temperature (85℃) |                  |

|------------|------------------------|------------------|-----------------------|------------------|

| Delisity   | I <sub>cc</sub>        | I <sub>ccq</sub> | I <sub>cc</sub>       | I <sub>ccq</sub> |

| 16GB (DDP) |                        |                  |                       |                  |

| 32GB (QDP) | 0                      | Typ. 150uA       | 0                     | Max. 650uA       |

| 64GB (ODP) |                        |                  |                       |                  |

ullet In Sleep state, triggered by CMD5, NAND  $V_{cc}$  power supply is switched off (CTRL  $V_{ccq}$  on)

• Not 100% tested.

# 4. e-NAND New features (eMMC5.0 and eMMC5.1)

#### 4.1 eMMC5.0 New features

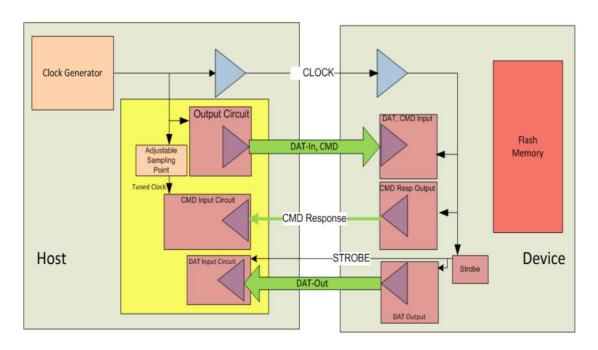

#### 4.1.1 HS400 mode

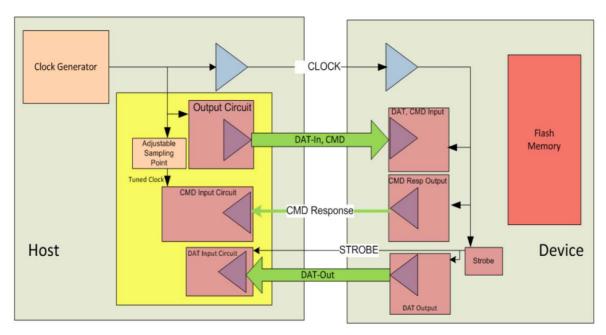

e-NAND supports HS400 signaling to achieve a bus speed of 400MB/s via a 200MHz DDR clock frequency. HS400 mode supports only 8-bit bus width and the 1.8V  $V_{ccq}$ . Due to the speed, the host may need to have an adjustable sampling point to reliably receive the incoming data (Read Data and CRC Response) with DS pin. e-NAND supports up to 5 Driver Strength.

| Driver type values | Support   | Nominal<br>Impedance | Approximated driving<br>capability compared to<br>Type_0 | Remark                                                                                    |

|--------------------|-----------|----------------------|----------------------------------------------------------|-------------------------------------------------------------------------------------------|

| 0                  | Mandatory | 50 <b>Ω</b>          | x 1                                                      | Default Driver Type. Supports up to 200MHz operation.                                     |

| 1                  |           | 33 <b>Ω</b>          | x 1.5                                                    | Supports up to 200MHz operation.                                                          |

| 2                  | Optional  | 66Ω                  | x 0.75                                                   | The weakest driver that supports up to 200MHz operation.                                  |

| 3                  | Ориона    | 100 <b>Ω</b>         | x 0.5                                                    | For low noise and low EMI systems. Maximal operating frequency is decided by host design. |

| 4                  |           | 40 <b>Ω</b>          | x 1.2                                                    |                                                                                           |

#### [Table 2] I/O Driver strength types

Selecting **HS\_Timing** depends on Host I/F speed, default is 0, but all of value can be selected by host.

| Value | Timing                                            | Supportability for e-NAND |

|-------|---------------------------------------------------|---------------------------|

| 0x00  | Selecting backward compatibility interface timing | Support                   |

| 0x01  | High speed                                        | Support                   |

| 0x02  | HS200                                             | Support                   |

| 0x03  | HS400                                             | Support                   |

[Table 3] HS\_Timing values

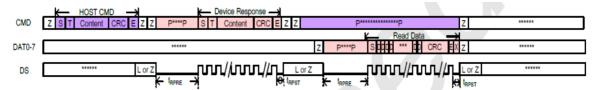

# 4.1.1.1 Bus timing specification in HS400 mode

# **■ HS400 Device input timing**

The CMD input timing for HS400 mode is the same as CMD input timing for HS200 mode.

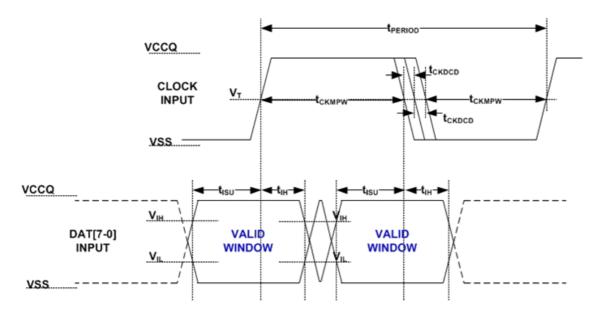

[Figure 4] HS400 Device input timing

| Parameter                     | Symbol              | Min   | Max | Unit | Remark                                                                                                        |

|-------------------------------|---------------------|-------|-----|------|---------------------------------------------------------------------------------------------------------------|

| Input CLK                     |                     |       |     | l    |                                                                                                               |

| Cycle time data transfer mode | t <sub>PERIOD</sub> | 5     |     |      | 200MHz(Max), between rising edges with respect to $V_{\text{T}}$                                              |

| Slew rate                     | SR                  | 1.125 |     | V/ns | With respect to V <sub>IH</sub> /V <sub>IL</sub>                                                              |

| Duty cycle<br>distortion      | t <sub>CKDCD</sub>  | 0.0   | 0.3 | ns   | Allowable deviation from an ideal 50% duty cycle. With respect to $V_{\text{T}}$ Includes jitter, phase noise |

| Minimum pulse width           | t <sub>CKMPW</sub>  | 2.2   |     | ns   | With respect to V <sub>T</sub>                                                                                |

| Input DAT (reference          | ced to CLK)         |       |     |      | ·                                                                                                             |

| Input set-up time             | t <sub>ISUddr</sub> | 0.4   |     | ns   | $C_{DEVICE} \le 6pF$<br>With respect to $V_{IH}/V_{IL}$                                                       |

| Input hold time               | t <sub>IHddr</sub>  | 0.4   |     | ns   | $C_{DEVICE} \le 6pF$<br>With respect to $V_{IH}/V_{IL}$                                                       |

| Slew rate                     | SR                  | 1.125 |     | V/ns | With respect to $V_{IH}/V_{IL}$                                                                               |

[Table 4] HS400 Device input timing

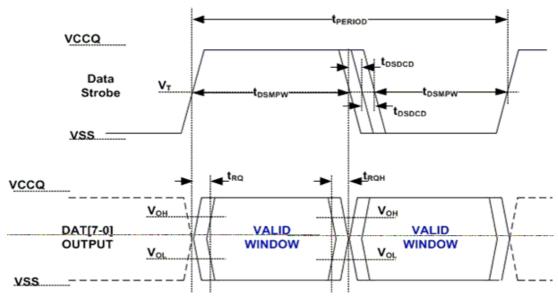

# **■** HS400 Device output timing

Data strobe is for reading data in HS400 mode. Data strobe is toggled only during data read or CRC status response.

[Figure 5] HS400 Device output timing

| Parameter                              | Symbol              | Min   | Max                       | Unit                | Remark                                                                                                                           |  |

|----------------------------------------|---------------------|-------|---------------------------|---------------------|----------------------------------------------------------------------------------------------------------------------------------|--|

| Input CLK                              |                     |       |                           |                     | ,                                                                                                                                |  |

| Cycle time data transfer mode          | t <sub>PERIOD</sub> | 5     |                           |                     | 200MHz(Max), between rising edges with respect to $V_{T}$                                                                        |  |

| Slew rate                              | SR                  | 1.125 |                           | V/ns                | With respect to V <sub>OH</sub> /V <sub>OL</sub> and HS400 reference load                                                        |  |

| Duty cycle<br>distortion               | t <sub>DSDCD</sub>  | 0.0   | 0.2                       | ns                  | Allowable deviation from the input CLK duty cycle distortion( $t_{CKDCD}$ ) With respect to $V_{T}$ Includes jitter, phase noise |  |

| Minimum pulse width                    | t <sub>DSMPW</sub>  | 2.0   |                           | ns                  | With respect to V <sub>T</sub>                                                                                                   |  |

| Read pre-amble                         | t <sub>RPRE</sub>   | 0.4   | 5 (One<br>Clock Cycle)    | t <sub>PERIOD</sub> | Max value is specified by manufacturer. value up to infinite is valid.                                                           |  |

| Read post-amble                        | t <sub>RPST</sub>   | 0.4   | 2.5 (Half<br>Clock Cycle) | t <sub>PERIOD</sub> | Max value is specified by manufacturer. value up to infinite is valid.                                                           |  |

| Output DAT (referenced to Data strobe) |                     |       |                           |                     |                                                                                                                                  |  |

| Output skew                            | t <sub>RQ</sub>     |       | 0.4                       | ns                  | With respect to $V_{OH}/V_{OL}$ and HS400 reference load                                                                         |  |

| Output hold skew                       | t <sub>RQH</sub>    |       | 0.4                       | ns                  | With respect to $V_{OH}/V_{OL}$ and HS400 reference load                                                                         |  |

| Slew rate                              | SR                  | 1.125 |                           | V/ns                | With respect to $V_{OH}/V_{OL}$ and HS400 reference load                                                                         |  |

[Table 5] HS400 Device output timing

| Parameter                             | Symbol              | Min | Туре | Max | Unit | Remark |

|---------------------------------------|---------------------|-----|------|-----|------|--------|

| Pull-up resistance for CMD            | R <sub>CMD</sub>    | 4.7 |      | 100 | Kohm |        |

| Pull-up resistance for DAT0-7         | R <sub>DAT</sub>    | 10  |      | 100 | Kohm |        |

| Pull-down resistance for Data strobe  | $R_{DS}$            | 10  |      | 100 | Kohm |        |

| Internal pull up resistance DAT1-DAT7 | R <sub>int</sub>    | 10  |      | 150 | Kohm |        |

| Bus signal line capacitance           | $C_L$               |     |      | 13  | pF   |        |

| Single Device capacitance             | C <sub>Device</sub> |     |      | 6   | pF   |        |

[Table 6] HS400 Device input timing

#### ■ Data Strobe for HS400

Data strobe is Return Clock signal used in HS400 mode. This signal is generated by the device and used for data output and CRC status response output in HS400 mode. The frequency of this signal follows the frequency of CLK. For data output each cycle of this signal directs two bits transfer(2x) on the data - one bit for positive edge and the other bit for negative edge. For CRC status response output, the CRC status is latched on the positive edge only, and don't care on the negative edge. Data strobe signal is toggled only for Data out and CRC response (Align CMD response as well as CRC response to the DS in eMMC5.1)

[Figure 6] HS400 Host and Device block diagram

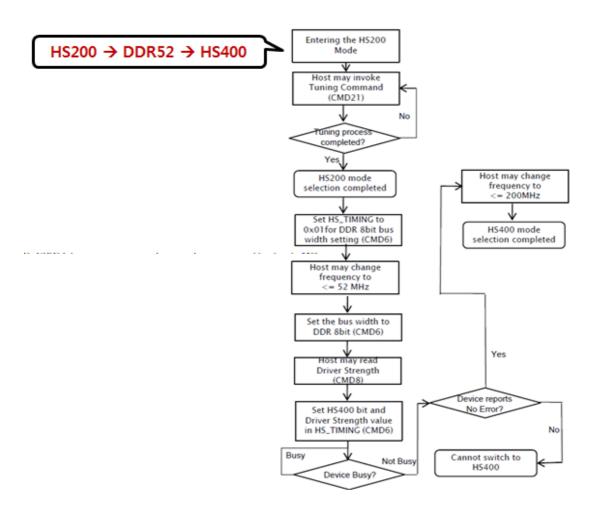

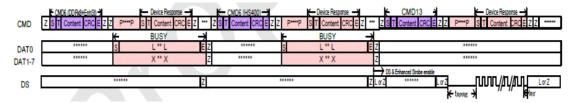

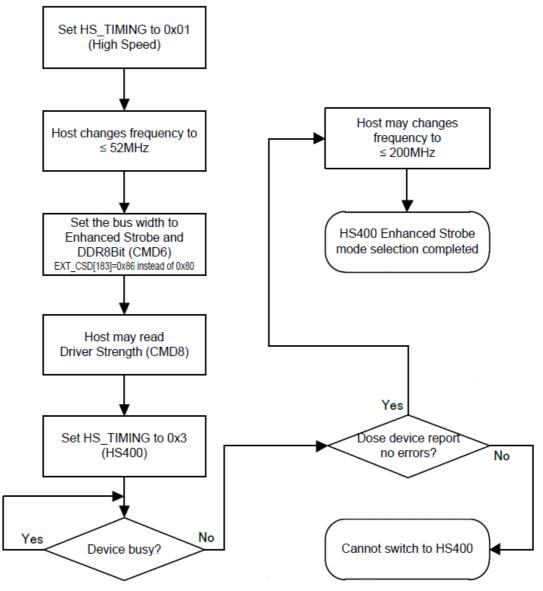

#### 4.1.1.2 HS400 Mode selection

Following JEDEC standard for eMMC5.0, changing bus mode directly from HS200 to HS400 is not allowed. It has a rule for changing bus width from SDR mode to DDR mode that HS\_TIMING must be set to "0x01"(HS mode: 52MHz) before setting BUS\_WIDTH for DDR operation. We recommend the HS400 bus mode selection sequence as following.

(eMMC5.1 has basically same flow, but 'enhanced strobe feature' is added. Please refer to 4.2.6 Enhanced strobe)

[Figure 7] HS400 Bus mode selection sequence

# **■ EXT\_CSD** register for Data strobe

# • Enhanced Strobe field in BUS\_WIDTH [183]

| Bit 7           | Bit 6 | Bit 5    | Bit 4 | Bit 3              | Bit 2 | Bit 1 | Bit 0 |

|-----------------|-------|----------|-------|--------------------|-------|-------|-------|

| Enhanced Strobe |       | Reserved |       | Bus Mode Selection |       |       |       |

BIT[7]: 0: Strobe is provided only during data out and CTC response [Default]

The support of STROBE\_ENHANCED mode is optional for devices. STROBE\_SUPPORT[184] register of EXT\_CSD indicates whether a device supports that mode.

<sup>1:</sup> Strobe is provided during data out, CRC response and CMD response

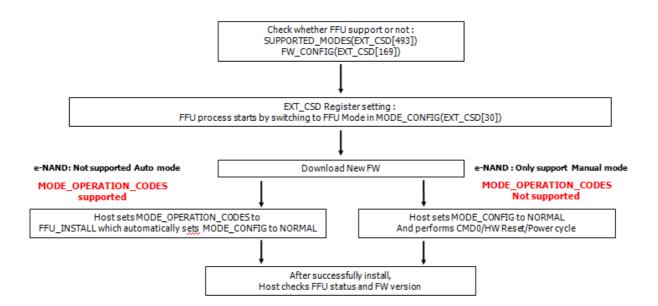

# 4.1.2 Field firmware update (FFU)

To download a new firmware, the e-NAND requires instruction sequence following JEDEC standard. SK hynix e-NAND only supports Manual mode (MODE\_OPERATION\_CODES is not supported). For more details, see as the following chart and register table given below.

[Figure 8] FFU flow chart

# 4.1.2.1 Field F/W update flow - CMD sequence

| Operation                    | CMD                    | Remark                                                                                         |  |

|------------------------------|------------------------|------------------------------------------------------------------------------------------------|--|

| Set bus width (1bit or 4bit) |                        | Bus width should be 1bit or 4bit                                                               |  |

| Set block length 512B        | CMD16, arg: 0x00000200 |                                                                                                |  |

| Enter FFU mode               | CMD6, arg: 0x031E0100  |                                                                                                |  |

| Send FW to device(Download)  | CMD25, arg: 0xFFFAFFF0 | Sending CMD25 is followed by sending FW data                                                   |  |

| CMD12 : Stop                 | CMD12, arg: 0x00000000 |                                                                                                |  |

| CMD6 : Exit FFU mode         | CMD6, arg: 0x031E0000  |                                                                                                |  |

| CMD0/HW Reset/Power cycle    |                        |                                                                                                |  |

| Re-Init to trans state       | CMD0, CMD1             |                                                                                                |  |

| Check if FFU is succeeded    | CMD8, arg: 0x00000000  | Check EXT_CSD[26]: FFU_SUCCESS If FFU_SUCCESS is 0, FFU is succeeded, otherwise FFU is failed. |  |

#### 4.1.2.2 EXT\_CSD Register for FFU

#### ■ SUPPORTED\_MODE[493] (Read Only)

BIT[0]: '0' FFU is not supported by the device. '1' FFU is supported by the device.

BIT[1]: '0' Vendor specific mode (VSM) is not supported by the device. '1' Vendor specific mode is supported by the device.

| Bit      | Field    | Supportability |

|----------|----------|----------------|

| Bit[7:2] | Reserved | -              |

| Bit[1]   | VSM      | Not support    |

| Bit[0]   | FFU      | Supported      |

# ■ FFU\_FEATURE[492] (Read Only)

BIT[0]: '0' Device does not support MODE\_OPERATION\_CODES field (Manual mode)

'1' Device supports MODE\_OPERATION\_CODES field (Auto mode)

| Bit      | Field                          | Supportability |

|----------|--------------------------------|----------------|

| Bit[7:1] | Reserved                       | -              |

| Bit[0]   | SUPPORTED_MODE_OPERATION_CODES | Not supported  |

# ■ FF\_ARG[490-487] (Read Only)

Using this field the device reports to the host which value the host should set as an argument for read and write commands is FFU mode.

# **■** FF\_CONFIG[169] (R/W)

BIT[0]: Update disable

0x0 : FW updates enabled. / 0x01 : FW update disabled permanently

| Bit      | Field          | Supportability           |

|----------|----------------|--------------------------|

| Bit[7:1] | Reserved       | -                        |

| Bit[0]   | Update disable | FW updates enabled (0x0) |

# ■ FFU\_STATUS[26] (R/W/E\_P)

Using this field the device reports to the host the state of HHU process.

| Value       | Description                   |

|-------------|-------------------------------|

| 0x13 ~ 0xFF | Reserved                      |

| 0x12        | Error in downloading Firmware |

| 0x11        | Firmware install error        |

| 0x10        | General error                 |

| 0x01 ~ 0x0F | Reserved                      |

| 0x00        | Success                       |

# ■ OPERATION\_CODES\_TIMEOUT[491](Read Only)

Maximum timeout for the SWITCH command when setting a value to the MODE\_OPERATION\_CODES field The register is set to '0', because the e-NAND doesn't support MODE\_OPERATION\_CODES.

| Value       | Description                                                                 | Timeout value   |

|-------------|-----------------------------------------------------------------------------|-----------------|

| 0x01 ~ 0x17 | MODE_OPERATION_CODES_TIMEOUT = 100us x 2 <sub>OPERATION_CODES_TIMEOUT</sub> | 0 (Not defined) |

| 0x18 ~ 0xFF | Reserved                                                                    | -               |

# ■ MODE\_OPERATION\_CODES[29] (W/E\_P)

The host sets the operation to be performed at the selected modes, in case MODE\_CONFIGS is set to FFU\_MODE, MODE\_OPERATION\_CODES could have the following values :

| Bit          | Description |

|--------------|-------------|

| 0x01         | FFU_INSTALL |

| 0x02         | FFU_ABOUT   |

| 0x00, others | Reserved    |

# 4.1.3 Health(Smart) report

Using this feature is for monitoring device status and preventing the error and failure in advance. Host can check device information with EXT\_CSD as the register table given below.

| Field                            | CSD slice | Description                                                                                                   |

|----------------------------------|-----------|---------------------------------------------------------------------------------------------------------------|

| VENDOR_PROPRIETARY_HEALTH_REPORT | [301:270] | Reserved for vendor proprietary health report. (NONE)                                                         |

| DEVICE_LIFE_TIME_EST_TYPE_ A/B   | [268:269] | Current average P/E cycle of memory of Type A(SLC) / Type B(MLC) relative to its maximum estimated capability |

| PRE_EOL_INFO                     | [267]     | Consumed reserved blocks to notify before reaching the EOL (End of life) status                               |

| OPTIMAL_TRIM/WRITE_READ_SIZE     | [264:266] | Minimum optimal (for the device) Erase / Write / Read unit size for the different partitions                  |

| DEVICE_VERSION                   | [263:262] | Device version                                                                                                |

| FIRMWARE_VERSION                 | [261:254] | Device FW version                                                                                             |

[Table 7] Using EXT\_CSD for health report (Read only)

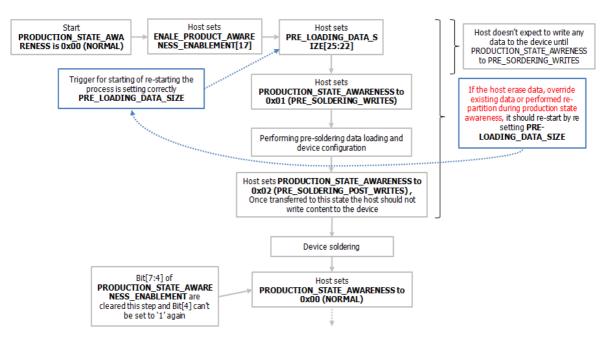

#### 4.1.4 Production state awareness

This new feature is added for eMMC5.0 JEDEC Spec. to prevent the data break during device soldering. For this feature implementation, e-NAND supports only manual mode and PRODUCT\_STATE\_AWARENESS\_TIMEOUT is 0x17(maximum). For more detail, see as the flow chart and register table given below.

[Figure 9] Production State Awareness manual mode flowchart

#### ■ PRODUCTION\_STATE\_AWARENESS\_TIMEOUT[218] (Read Only)

This field indicates maximum timeout for the SWITCH command when setting a value to the  $PRODUCTION\_STATE\_AWARENESS[133]$  field

| Value       | Description                                                                        | Timeout value  |

|-------------|------------------------------------------------------------------------------------|----------------|

| 0x01 ~ 0x17 | Production State Timeout = 100us x 2 <sub>PRODUCTION_STATE_AWARENESS_TIMEOUT</sub> | 0x17 (838.86s) |

| 0x18 ~ 0xFF | Reserved                                                                           | -              |

# ■ PRODUCTION\_STATE\_AWARENESS[133](R/W/E)

e-NAND doesn't support 0x03 state.

| Value       | Device State                          | Description                                                                    |

|-------------|---------------------------------------|--------------------------------------------------------------------------------|

| 0x00        | NORMAL (Field)                        | Regular operation                                                              |

| 0x01        | PRE_SOLDERING_WRITES                  | -                                                                              |

| 0x02        | PRE_SOLDERING_POST_WRITES             | Once transferred to this state the host should not write content to the device |

| 0x03        | AUTO_PRE_SOLDERING                    | Not supported                                                                  |

| 0x04 ~ 0x0F | Reserved                              | -                                                                              |

| 0x10 ~ 0x1F | Reserved for Vendor Proprietary Usage | -                                                                              |

# ■ PRODUCTION\_STATE\_ENABLEMENT[17]

e-NAND only supports manual mode for PRODUCTION\_STATE\_AWARENESS

|                                                                                                                                        | Enablement(R/W/E) |      |                                            |      | Capab | ilities(R)               |                          |

|----------------------------------------------------------------------------------------------------------------------------------------|-------------------|------|--------------------------------------------|------|-------|--------------------------|--------------------------|

| Bit7                                                                                                                                   | Bit6              | Bit5 | Bit4                                       | Bit3 | Bit2  | Bit1                     | Bit0                     |

| Rese                                                                                                                                   | rved              | Mode | Production<br>State<br>Awareness<br>enable | Rese | erved | Auto mode<br>Supported   | Manual mode<br>Supported |

| Cleared when PRODUCTION_STATE_AWARENESS is charged to Normal (either automatically or by setting PRODUCTION_STATE_AWARENESS to Normal) |                   |      |                                            |      |       | e set to '1' only<br>nce |                          |

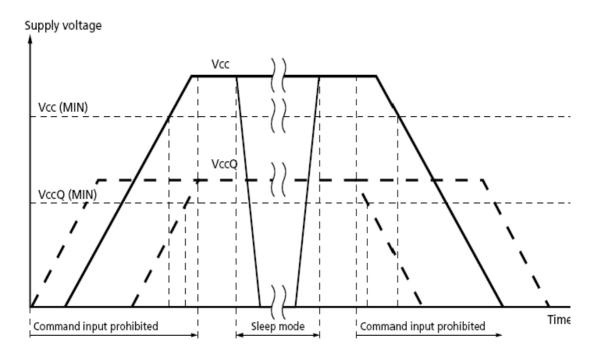

# 4.1.5 Sleep notification

Host may use to a power off notification when it intends to turn-off  $V_{cc}$  After moving the device to sleep state. Some features are added to clarify the spec for entering sleep mode when power off notification is enabled.

# ■ Add the SLEEP\_NOTIFICATION on the interruptible Command List

| CMD  | Description                                                                     | Is interruptible? |

|------|---------------------------------------------------------------------------------|-------------------|

| CMD6 | SWITCH, Byte POWER_OFF_NOTIFICATION, Value POWER_OFF_LONG or SLEEP_NOTIFICATION | Yes               |

# ■ SLEEP\_NOTIFICATION\_TIME[216](Read Only)

Maximum timeout for the SWITCH command when notifying the device that it is about to move to sleep state by writing SLEEP\_NOTIFICATION to POWER\_OFF\_NOTIFICATION[34]byte. (unit : 10us)

| Value       | Description                                                              | Timeout value |

|-------------|--------------------------------------------------------------------------|---------------|

| 0x01 ~ 0x17 | Sleep Notification Timeout = 10us x 2 <sub>SLEEP_NOTIFICATION_TIME</sub> | 0xC (40.96ms) |

| 0x18 ~ 0xFF | Reserved                                                                 | -             |

# **■** POWER\_OFF\_NOTIFICATION[34]

Add Ox04h for the SLEEP\_NOTIFICATION as a valid value

| Value | Field              | Description                                                                                        |

|-------|--------------------|----------------------------------------------------------------------------------------------------|

| :     | :                  | :                                                                                                  |

| 0x03  | POWER_OFF_LONG     | Host is going to power off the device. The device shall respond within POWER_OFF_LONG_TIME         |

| 0x04  | SLEEP_NOTIFICATION | Host is going to put device in sleep mode. The device shall respond within SLEEP_NOTIFICATION_TIME |

# 4.1.6 Secure removal type

This feature is used for how information is removed from the physical memory during a purge operation.

#### ■ Secure Removal Type[16]

Among four options for secure removal type, e-NAND supports 0x3, 0x1 and 0x0 (0x2 option is not supported) e-NAND recommends using a vendor defined removal type(type 3). If host want to erase the device physically using removal type0. Secure erase & Secure trim time is longer than using removal type0

| ВІТ      | Description of Secure<br>Removal Type |        | Supportability                                                                                                          |             |

|----------|---------------------------------------|--------|-------------------------------------------------------------------------------------------------------------------------|-------------|

|          |                                       | 0x3    | Information removed using a vendor defined                                                                              | Support     |

|          | Configure Secure Removal              | 0x2    | Information removed by an overwriting the addressed locations with a character, its complement, then a random character | -           |

| BIT[5:4] | Type (R/W)                            | 0x1    | Information removed by an overwriting the addressed locations with a character followed by an erase                     | -           |

|          |                                       | 0x0    | Information removed by an erase of the physical memory                                                                  | -           |

|          |                                       | BIT[3] | Information removed using a vendor defined                                                                              | Support     |

|          | Supported Secure Removal              | BIT[2] | Information removed by an overwriting the addressed locations with a character, its complement, then a random character | Not support |

| BIT[3:0] | Type (R)                              | BIT[1] | Information removed by an overwriting the addressed locations with a character followed by an erase                     | Support     |

|          |                                       | BIT[0] | Information removed by an erase of the physical memory                                                                  | Support     |

# 4.2 eMMC5.1 New features

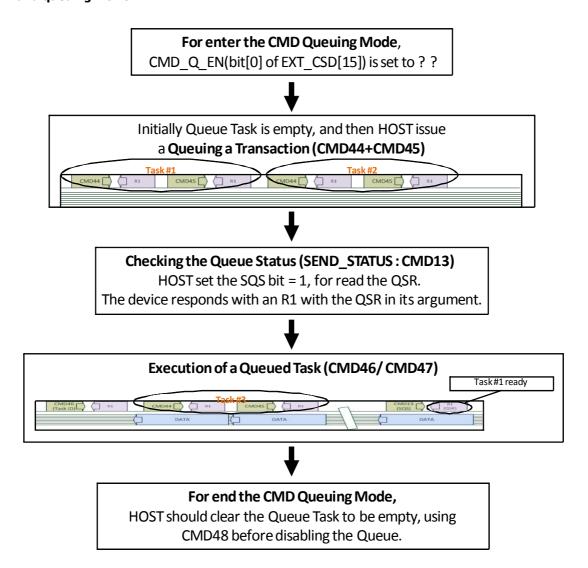

# 4.2.1 Command queuing

e-NAND manages an internal task queue to which the host can queue data transfer tasks to efficient operate.

# 4.2.1.1 CMD list for Command queuing

| Index | Abbreviation          | Argument                                                                                                                                                                                              | Remark                                                                                                                                                                              |

|-------|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CMD44 | Queued Task parameter | [31] Reliable Write Request [30] Data Direction (Read=1, Write=0) [29] Tag Request [28:25] context ID [24]Forced Programming [23] Priority ( simple =0, high=1) [20:16] Task ID(31~0) [15:0] # of BLK | Encodes parameter which are necessary for queuing the task and executing the transfer                                                                                               |

| CMD45 | Queued Task Address   | [31:0] Block address for the transaction                                                                                                                                                              | The host instructs the device to queue a data transfer task                                                                                                                         |

| CMD46 | Execute Read Task     | [20:16] Task ID of the                                                                                                                                                                                | In order to execute a data read task                                                                                                                                                |

| CMD47 | Execute Write Task    | requested task which is must marked as<br>"ready for execution" in the Queue Status<br>Register                                                                                                       | (CMD46) or write task(CMD47) which is already queued                                                                                                                                |

| CMD48 | CMDQ_TASK_MGMT        | [31:21] reserved<br>[20:16]: TaskID<br>[15:4]: reserved<br>[3:0] TM op-code                                                                                                                           | Device shall discard a specific task or entire queue (all tasks in the queue) [20:16] when TM op-code = 2h these bits represent TaskID. When TM op-code=1h these bits are reserved. |

| Index | Abbreviation | Argument                                                     | Remark                                                                                                                                         |

|-------|--------------|--------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|

| CMD13 | SEND_STATUS  | [31:16] RCA<br>[15] <b>SQS</b><br>[14] Stuff bits<br>[0] HPI | In case SQS bit = 1: indicate that this is CMD13 of CMD Queue. In response device shall send the QSR. In this case HPI bit muse be set to '0'. |

#### 4.2.1.2 EXT\_CSD Register for Command queuing

#### ■ CMDQ\_SUPPORT[308](Read only)

This field indicates whether command queuing is supported by the device.

BIT[0]: 0: Command queuing is not supported

1: Command queuing is supported

| Bit      | Field        | Supportability  |

|----------|--------------|-----------------|

| Bit[7:1] | Reserved     | -               |

| Bit[0]   | CMDQ Support | Supported (0x1) |

#### ■ CMDQ\_DEPTH[307](Read only)

This field is used to calculate the depth of the queue supported by the device. The maximum depth allowed by the standard is 32. The range of allowed Task IDs is 0 through N.

BIT[4:0]: N, a parameter used to calculate the Queue Depth of task queue in the device.

Queue Depth = N+1.

| Bit      | Field    | CMD queue depth value |

|----------|----------|-----------------------|

| Bit[7:5] | Reserved | -                     |

| Bit[4:0] | N        | N=31 (0x1F)           |

#### ■ CMDQ\_MODE\_EN[15](R/W)

This field is used by the host enable command queuing mechanism if supported by the device.

BIT[0]: 0: Command queuing is disabled. Host should clear the queue empty using CMD48 prior disabling the queue.

1: Command queuing is enabled

| Bit      | Field       | Supportability |

|----------|-------------|----------------|

| Bit[7:1] | Reserved    | -              |

| Bit[0]   | CMDQ enable | -              |

To maintain backward compatibility with hosts, which do not support command queuing, when the command queuing is disabled other functionality of the device is as if the device does not support command queuing.

#### 4.2.1.3 New register for Command queuing

# ■ QSR (Queue Status Register)

The 32bit QSR carries the state of tasks in the queue at a specific point in time.

The host has read access to this register through device response to SEND\_STATUS command(CMD13 with bit[15]="1"), R1's argument will be the QSR.

Every bit in the QSR represents the task who's ID corresponds to the bit index.

If bit QSR[i]='0', the queued task with a Task ID i is not ready for execution.

The task may be queued and pending, or the Task ID is unused.

If bit QSR[i]='1', the queued task with Task ID i is ready for execution.

#### 4.2.1.4 Command queuing Flows

#### 4.2.2 Cache Barrier

There are cases where the host is not interested in flushing the data right away, however it would like to keep an order between different cached data.

The flushing can be delayed by the device to some later idle time. Barrier commands avoid the long delay by flush commands.

Arrival sequence

#### 4.2.2.1 EXT\_CSD Register for Cache Barrier

# ■ BARRIER\_SUPPORT[488](Read only)

This field indicates whether the device supports the barrier command.

BIT[7:0]: 0: Barrier command is not supported

1: Barrier command is supported

| Bit      | Field           | Supportability  |

|----------|-----------------|-----------------|

| Bit[7:0] | BARRIER_SUPPORT | Supported (0x1) |

#### ■ FLUSH\_CACHE[32](W/E\_P)

A barrier command is issued by setting BARRIER bit. All data cached before the barrier shall be flushed to the non-volatile memory before any request after the barrier command.

Data in the cache shall be flushed to the non-volatile storage by setting the FLUSH bit.

BIT[1]: 0: Reset value 1: Set barrier

BIT[0]: 0: Reset value

1: Triggers the flush

| Bit      | Field    | Supportability |

|----------|----------|----------------|

| Bit[7:2] | Reserved | -              |

| Bit[1]   | BARRIER  | -              |

| Bit[0]   | FLUSH    | -              |

# ■ BARRIER\_CTRL[31](R/W)

This field is used by the host enable barrier command mechanism if supported by the device.

BIT[0]: 0: Barrier feature is OFF

1: Barrier feature is ON

| Bit      | Field      | Supportability |

|----------|------------|----------------|

| Bit[7:1] | Reserved   | -              |

| Bit[0]   | BARRIER_EN | -              |

#### 4.2.2.2 Cache barrier Flows

# 1. Support Barrier command

- The device exposes its barrier support capability via the BARRIER\_SUPPORT (EXT\_CSD byte [486])

#### 2. Enable Barrier command

- The host shall set bit 0 of BARRIER\_EN (EXT\_CSD byte [31])

- 3. Cache on

- 4. Send data

#### 5. Set Barrier

- The host shall set both BARRIER bit and FLUSH bit of the FLUSH\_CACHE (EXT\_CSD byte [32])

# 4.2.3 Cache Flushing Report

For devices which flush cached data in an in-order manner, cache barrier commands are redundant and impose a needless overhead to the device and host.

#### 4.2.3.1 EXT\_CSD Register for Cache Flushing Report

#### ■ CACHE\_FLUSH\_POLICY[240](Read only)

BIT[0]: 0: Device flushing policy is not provided by the device.

1: Device is using a FIFO policy for cache flushing

| Bit      | Field    | Supportability   |

|----------|----------|------------------|

| Bit[7:1] | Reserved | -                |

| Bit[0]   | FIFO     | Supported (0x01) |

#### 4.2.4 BKOP Control

This feature allows the host to indicate to the device if it is expected to periodically manually start background operations by writing to the BKOPS\_START field.

#### 4.2.4.1 EXT\_CSD Register for BKOP Control

#### **■** BKOP\_EN[163](R/W/E, R/W)

BIT[1](R/W/E): 0: Device shall not perform background operations while not servicing the host.

1: Device may perform background operations while not servicing the host.

BIT[0] (R/W): 0: Host does not support background operations handling and is not expected to write to BKOPS\_START field.

1: Host is indicating that it shall periodically write to BKOPS START field to manually start background operations.

| Bit      | Field     | Supportability |

|----------|-----------|----------------|

| Bit[7:2] | Reserved  | -              |

| Bit[1]   | AUTO_EN   | -              |

| Bit[0]   | MANUAL_EN | -              |

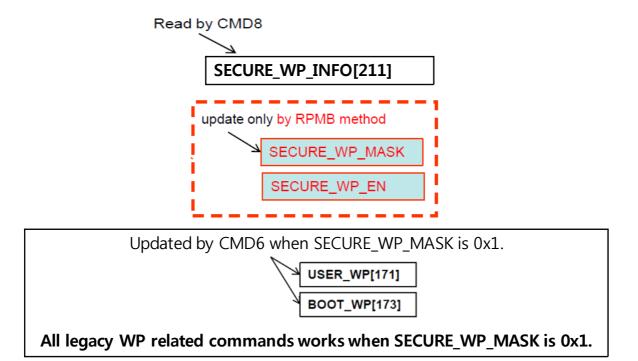

#### 4.2.5 Secure Write Protection

Any application running on the host may issue write protection by updating fields of write protection related EXT\_CSD, like USER\_WP[171], BOOT\_WP[173], by issuing CMD6, CMD8, CMD28 and CMD29 (Legacy mode).

However there are weak points in the legacy mode. To prevent un-authorized changes, host should enter the secure write protect mode

- In Secure WP Mode, WP related EXT\_CSDs (EXT\_CSD[171],[173]) can be updated only if SECURE\_WP\_MASK fields is 0x1.

- Secureness is provided by allowing only RPMB method to update the register for SECURE\_WP\_MASK.

- Automatic Write protection mode is added to prevent security hole by power-control security attack.

#### 4.2.5.1 EXT\_CSD Register for Secure Write Protection

#### ■ SECURE\_WP\_INFO[211](Read Only)

The SECURE\_WP\_SUPPORT field indicates whether the device is supporting secure write protection mode. The SECURE\_WP\_EN\_STATUS is showing the value of SECURE\_WP\_EN defined in Authenticated Device Configuration Area.

BIT[1] 0: Legacy Write Protection mode 1: Secure Write Protection mode

BIT[0] 0: Secure Write Protection is NOT supported by this device

1: Secure Write Protection is supported by this device

| Bit      | Field               | Supportability   |

|----------|---------------------|------------------|

| Bit[7:2] | Reserved            | -                |

| Bit[1]   | SECURE_WP_EN_STATUS | -                |

| Bit[0]   | SECURE_WP_SUPPROT   | Supported (0x01) |

#### 4.2.5.2 New register for Secure Write Protection

#### ■ Authenticated Device Configuration Area

- Hidden register instead of EXT\_CSD register for SECURE\_WP\_MODE\_CONFIG, ENABLE.

- Those two SECURE\_WP\_MODE\_CONFIG and SECURE\_WP\_MODE\_ENABLE registers are defined in Device Configuration area, and those register should be updated only by Authenticated Device Configuration write request. (RPMB)

| Name                               | Field                 | Size (Bytes) | Cell Type | Address |

|------------------------------------|-----------------------|--------------|-----------|---------|

| Reserved                           |                       | 253          | -         | [255:3] |

| Secure Write Protect Configuration | SECURE_WP_MODE_CONFIG | 1            | R/W/E_P   | [2]     |

| Secure Write Protect Enable        | SECURE_WP_MODE_ENABLE | 1            | R/W/E     | [1]     |

| Reserved                           |                       | 1            |           | [0]     |

# ■ Authenticated Device Configuration Area (1): SECURE\_WP\_MODE\_ENABLE (R/W/E)

The byte is to enter/exit the secure write protection mode.

If host want a device to enter the secure Write Protection mode, host set the SECURE\_WP\_EN bit as '0x1' in this register using Authenticated Device Configuration Write request. This register can be read using Authenticated Device Configuration Read request. If there are already write protected groups or write protected boot partitions, those will be preserved when entering or exiting secure Write protected mode.

Bit [0] 0: Legacy Write Protection mode.

(TMP\_WRITE\_PROTECT[12], PERM\_WRITE\_PROTECT[13] is updated by CMD27. USER\_WP[171], BOOT\_WP[173] and BOOT\_WP\_STATUS[174] are updated by CMD6.)

1: Secure Write Protection mode.

(The access to the write protection related EXT\_CSD and CSD fields depends on the value of SECURE\_WP\_MASK bit in SECURE\_WP\_MODE\_CONFIG field.)

The default value of this field is 0x0.

| Bit      | Field                 | Supportability |

|----------|-----------------------|----------------|

| Bit[7:1] | Reserved              | -              |

| Bit[0]   | SECURE_WP_MODE_ENABLE | -              |

#### ■ Authenticated Device Configuration Area (2): SECURE \_WP\_MODE\_CONFIG (R/W/E\_P)

In secure write protected mode, the updatability of USER\_WP[171], BOOT\_WP[173], TMP\_WRITE\_PROTECT[12] and PERM\_WRITE\_PROTECT[13] are controlled by this mask value.

- Bit [0] 0: Disabling updating WP related EXT\_CSD and CSD fields. CMD27 (Program CSD) will generate generic error for setting TMP\_WRITE\_PROTECT[12], PERM\_WRITE\_PROTECT[13]. CMD6 for updating USER\_WP[171], BOOT\_WP[173] and BOOT\_WP\_STATUS[174] generates SWITCH\_ERROR. If a force erase command is issued, the command will fail (Device stays locked) and the LOCK\_UNLOCK\_FAILED error bit will be set in the status register. If CMD28 or CMD29 is issued, then generic error will be occurred. Power-on Write Protected boot partitions will keep protected mode after power failure, H/W reset assertion and any CMD0 reset. The device keeps the current value of BOOT\_WP in the EXT\_CSD register to be same after power cycle, H/W reset assertion, and any CMD0 reset.

- 1: Enabling updating WP related EXT\_CSD and CSD fields.

(TMP\_WRITE\_PROTECT[12], PERM\_WRITE\_PROTECT[13], USER\_WP[171], BOOT\_WP[173] and BOOT\_WP\_STATUS[174] are accessed using CMD6, CMD8 and CMD27. If a force erase command is issued and accepted, then ALL THE DEVICE CONTENT WILL BE ERASED including the PWD and PWD\_LEN register content and the locked Device will get unlocked. If a force erase command is issued and power-on protected or a permanently-write-protected write protect groups exist on the device, the command will fail (Device stays locked) and the LOCK\_UNLOCK\_FAILED error bit will be set in the status register. An attempt to force erase on an unlocked Device will fail and LOCK\_UNLOCK\_FAILED error bit will be set in the status register. Write Protection is applied to the WPG indicated by CMD28 with the WP type indicated by the bit[2] and bit[0] of USER\_WP[171]. All temporary WP Groups and power-on Write Protected boot partitions become writable/erasable temporarily which means write protect type is not changed. All power-on and permanent WP Groups in user area will not become writable/erasable temporarily. Those temporarily writable/erasable area will become write protected when this bit is cleared to 0x0 by the host or when there is power failure, H/W reset assertion and any CMD0 reset. The device keeps the current value of BOOT\_WP CSD register to be same after power cycle, H/W reset assertion, and any CMD0 reset.)

The default value of this field is 0x0.

| Bit      | Field                 | Supportability |

|----------|-----------------------|----------------|

| Bit[7:1] | Reserved              | -              |

| Bit[0]   | SECURE_WP_MODE_CONFIG | -              |

Rev 1.3 / Jul. 2015

# 4.2.5.3 RPMB Types for accessing Authenticated Device Configuration Area

Secure WP Enable & Configuration registers are defined in Authenticated Device Configuration Area which only can be accessible by new RPMB operations.

| Request M  | Request Message Types                             |  |  |  |  |  |

|------------|---------------------------------------------------|--|--|--|--|--|

| 0x0001     | Authentication key programming request            |  |  |  |  |  |

| 0x0002     | Reading of the Write Counter value –request       |  |  |  |  |  |

| 0x0003     | Authenticated data write request                  |  |  |  |  |  |

| 0x0004     | Authenticated data read request                   |  |  |  |  |  |

| 0x0005     | Result read request                               |  |  |  |  |  |

| 0x0006     | Authenticated Device Configuration Write request  |  |  |  |  |  |

| 0x0007     | Authenticated Device Configuration Read request   |  |  |  |  |  |

| Response N | Message Types                                     |  |  |  |  |  |

| 0x0100     | Authentication key programming response           |  |  |  |  |  |

| 0x0200     | Reading of the Write Counter value –response      |  |  |  |  |  |

| 0x0300     | Authenticated data write response                 |  |  |  |  |  |

| 0x0400     | Authenticated data read response                  |  |  |  |  |  |

| 0x0600     | Authenticated Device Configuration Write response |  |  |  |  |  |

| 0x0700     | Authenticated Device Configuration Read response  |  |  |  |  |  |

### 4.2.6 Enhanced strobe

In Enhanced Strobe mode DATA OUT, CRC Response and CMD Response are all synched to STROBE clocks. The timing relation between CMD Response output signals and STROBE clocks is the same as defined for DATA Out to STROBE clocks.

[Figure 10] HS400 Host and Device block diagram (when Enhanced Strobe is enabled)

Rev 1.3 / Jul. 2015

[Figure 11] Enhanced Strobe signals for CMD Response and Data Out (Read operation)

[Figure 12] Enhanced Strobe signals for CMD Response and Data Out (Read operation)

[Figure 13] HS400 mode change with Enhanced Strobe

### 4.2.6.1 EXT\_CSD Register for Enhanced Strobe

## ■ STROBE\_SUPPORT[184](Read only)

This register indicates whether a device supports Enhanced Strobe mode for operation modes that STROBE is used for HS400.

BIT[7:0]: 0: Indicates No support of Enhanced Strobe mode

1: Indicates the device supports Enhanced Strobe mode

| Bit      | Field          | Supportability   |

|----------|----------------|------------------|

| Bit[7:0] | STROBE_SUPPORT | Supported (0x01) |

#### 4.2.6.2 HS400 mode (Enhanced Strobe) selection

This selection flow describes how to initialize the eMMC device in HS400 mode while enabling Enhanced Strobe without the need for tuning procedure.

After the host initializes the device, host check whether the device supports the HS400 mode and Enhanced Strobe by reading the DEVICE\_TYPE and STROBE\_SUPPORT fields in the Extended CSD register.

After power-on or software reset (CMD0), the interface timing of the device is set as the default 'Backward Compatible Timing'. In order to switch to HS400 mode with Enhanced Strobe, host should perform the following steps.

[Figure 14] HS400 Bus mode (Enhanced Strobe) selection flow diagram

## 4.2.7 RPMB throughput improvement

This feature is proposed for RPMB write data size to improve the RPMB throughput in eMMC5.1 spec. In the eMMC5.0 spec, REL\_WR\_SEC\_C[222] register shall be set to 1 (hence the granularity is always 512B.)

- For reliable write to RPMB partition, there is limitation that block count can not exceed the size of REL\_WR\_SEC\_C x 512B. In eMMC5.1, the supported RPMB write access size is 256B, 512B, and 8KB.

#### ■ WRITE\_REL\_PARAM (EXT\_CSD[166]): Read only

#### When EXT\_CSD[166][4] (R) = 0

- Device does not support large RPMB wirte transfer

- The behavior is same as eMMC v5.0 or earlier

#### When $EXT_CSD[166][4](R) = 1$

- Device supports large RPMB wirte transfer

- Host transfers small RPMB write with block count = 1 or 2 (256/512B)

- Host transfers large RPMB write with block count = 32 (8KB)

- \* the start address should be 8KB aligned, and the transferred data (8KB) is all-new or all-old

| Bit    | Field          | Supportability   |

|--------|----------------|------------------|

| Bit[4] | EN_RPMB_REL_WR | Supported (0x01) |

# 5. e-NAND general parameters

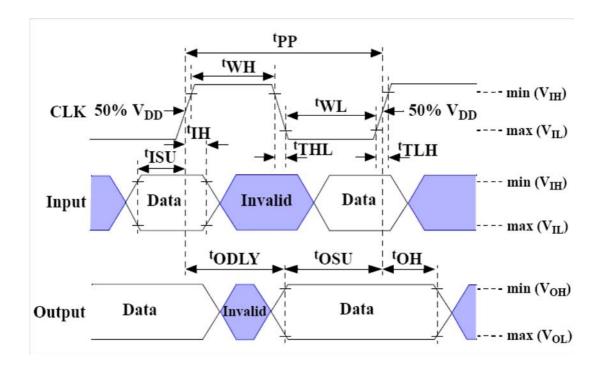

# **5.1 Timing**

## 5.1.1 Bus timing

Data must always be sampled on the rising edge of the clock.

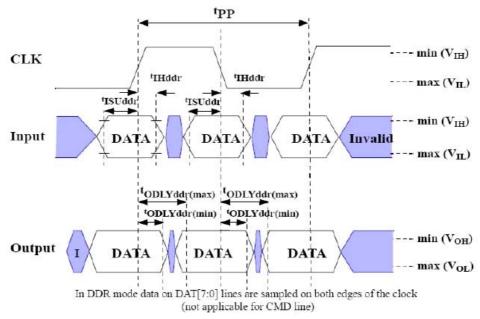

[Figure 15] Timing diagram: data input/output

| Parameter                                | Symbol            | Min | Max      | Unit | Remark                                      |

|------------------------------------------|-------------------|-----|----------|------|---------------------------------------------|

| Clock CLK                                | 1                 |     | <b>-</b> | •    |                                             |

| Clock frequency data transfer mode (PP)  | f <sub>PP</sub>   | 0   | 52       | MHz  | C <sub>L</sub> ≤30 pF<br>Tolerance: +100KHz |

| Clock frequency identification mode (OD) | f <sub>OD</sub>   | 0   | 400      | MHz  | Tolerance: +20KHz                           |

| Clock high time                          | t <sub>WH</sub>   | 6.5 |          | ns   | C <sub>L</sub> ≤ 30 pF                      |

| Clock low time                           | t <sub>WL</sub>   | 6.5 |          | ns   | C <sub>L</sub> ≤ 30 pF                      |

| Clock rise time                          | t <sub>TLH</sub>  |     | 3        | ns   | C <sub>L</sub> ≤ 30 pF                      |

| Clock fall time                          | t <sub>THL</sub>  |     | 3        | ns   | C <sub>L</sub> ≤ 30 pF                      |

| Inputs CMD, DAT (referenced to CLK)      | 1                 |     | -1       | •    |                                             |

| Input set-up time                        | t <sub>ISU</sub>  | 3   |          | ns   | C <sub>L</sub> ≤ 30 pF                      |

| Input hold time                          | t <sub>IH</sub>   | 3   |          | ns   | C <sub>L</sub> ≤ 30 pF                      |

| Outputs CMD, DAT (referenced to CLK)     | 1                 |     | <b>-</b> | •    |                                             |

| Output delay time during data transfer   | t <sub>ODLY</sub> |     | 13.7     | ns   | C <sub>L</sub> ≤ 30 pF                      |

| Output hold time                         | t <sub>OH</sub>   | 2.5 |          | ns   | C <sub>L</sub> ≤ 30 pF                      |

| Signal rise time                         | t <sub>RISE</sub> |     | 3        | ns   | C <sub>L</sub> ≤ 30 pF                      |

| Signal fall time                         | t <sub>FALL</sub> |     | 3        | ns   | C <sub>L</sub> ≤ 30 pF                      |

## [Table 9] High-speed e-NAND interface timing

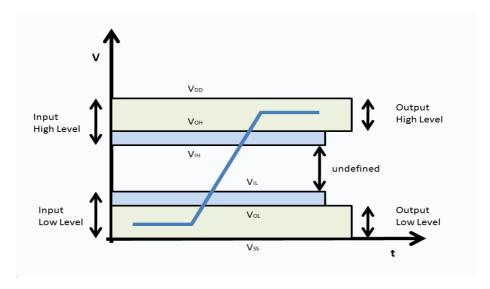

- CLK timing is measured at 50% of VDD.

- e-NAND shall support the full frequency range from 0-26Mhz, or 0-52MHz

- $\bullet$  CLK rising and falling times are measured by min (V  $_{IH})$  and max (V  $_{IL}).$

- Input CMD, DAT rising and falling times are measured by min  $(V_{IH})$  and max  $(V_{IL})$ , and output CMD, DAT rising and falling times are measured by min  $(V_{OH})$  and max  $(V_{OL})$ .

| Parameter                                | Symbol           | Min  | Max | Unit | Remark                 |  |  |  |  |

|------------------------------------------|------------------|------|-----|------|------------------------|--|--|--|--|

| Clock CLK                                | Clock CLK        |      |     |      |                        |  |  |  |  |

| Clock frequency data transfer mode (PP)  | f <sub>PP</sub>  | 0    | 26  | 400  | C <sub>L</sub> ≤30 pF  |  |  |  |  |

| Clock frequency identification mode (OD) | f <sub>OD</sub>  | 0    | 400 | MHz  |                        |  |  |  |  |

| Clock high time                          | t <sub>WH</sub>  | 10   |     | ns   | C <sub>L</sub> ≤ 30 pF |  |  |  |  |

| Clock low time                           | t <sub>WL</sub>  | 10   |     | ns   | CL ≤ 30 pF             |  |  |  |  |

| Clock rise time                          | t <sub>TLH</sub> |      | 10  | ns   | CL ≤ 30 pF             |  |  |  |  |

| Clock fall time                          | t <sub>THL</sub> |      | 10  | ns   | CL ≤ 30 pF             |  |  |  |  |

| Inputs CMD, DAT (referenced to CLK)      |                  |      | •   | 1    | -                      |  |  |  |  |

| Input set-up time                        | t <sub>ISU</sub> | 3    |     | ns   | CL ≤ 30 pF             |  |  |  |  |

| Input hold time                          | t <sub>IH</sub>  | 3    |     | ns   | CL ≤ 30 pF             |  |  |  |  |

| Outputs CMD, DAT (referenced to CLK)     |                  |      |     |      |                        |  |  |  |  |

| Output set-up time                       | t <sub>OSU</sub> | 11.7 |     | ns   | CL ≤ 30 pF             |  |  |  |  |

| Output hold time                         | t <sub>OH</sub>  | 8.3  |     | ns   | CL ≤ 30 pF             |  |  |  |  |

[Table 10] Backward-compatible e-NAND interface timing

- e-NAND must always start with the backward-compatible interface timing. The timing mode can be switched to high-speed timing by the host sending the switch command (CMD6) with the argument for high speed interface select.

- CLK timing is measured at 50% of VDD.

- ullet CLK rising and falling times are measured by min (V<sub>IH</sub>) and max (V<sub>IL</sub>).

- t<sub>OSU</sub> and t<sub>OH</sub> are defined as values from clock rising edge. However, there may be cards or devices which utilize clock falling edge to output data in backward compatibility mode.

Therefore, it is recommended for hosts either to set  $t_{WL}$  value as long as possible within the range which should not go over  $t_{CK}$ - $t_{OH}$ (min) in the system or to use slow clock frequency, so that host could have data set up margin for those devices. In this case, each device which utilizes clock falling edge might show the correlation either between  $t_{WL}$  and  $t_{OSU}$  or between  $t_{CK}$  and  $t_{OSU}$  for the device.

### 5.1.2 Bus timing for DAT Signals During 2x Data Rate Operation

These timings apply to the DAT[7:0] signals only when the device is configured for dual data mode operation. In dual data mode, the DAT signals operate synchronously of both the rising and the falling edges of CLK.

[Figure 16] Timing diagram: data input/output in dual data rate mode

| Parameter                               | Symbol               | Min.     | Max. | Unit | Remark                       |

|-----------------------------------------|----------------------|----------|------|------|------------------------------|

| Input CLK <sup>(1)</sup>                |                      |          |      |      |                              |

| Clock duty cycle                        |                      | 45       | 55   | %    | Includes jitter, phase noise |

| Clock rise time                         | t <sub>TLH</sub>     |          | 3    | ns   | CL≤30 pF                     |

| Clock fail time                         | t <sub>THL</sub>     |          | 3    | ns   | CL≤30 pF                     |

| Input CMD (referenced to CLK-SDR mode)  | )                    | l .      |      |      |                              |

| Input set-up time                       | t <sub>ISUddr</sub>  | 3        |      | ns   | CL≤20 pF                     |

| Input hold time                         | t <sub>IHDDR</sub>   | 3        |      | ns   | CL≤20 pF                     |

| Output CMD (referenced to CLK-SDR mod   | e)                   | l .      |      |      |                              |

| Output delay time during data transfer  | t <sub>ODLY</sub>    |          | 13.7 | ns   | CL≤20 pF                     |

| Output hold time                        | t <sub>OH</sub>      | 2.5      |      | ns   | CL≤20 pF                     |

| Signal rise time                        | t <sub>RISE</sub>    |          | 3    | ns   | CL≤20 pF                     |

| Signal fall time                        | t <sub>FALL</sub>    |          | 3    | ns   | CL≤20 pF                     |

| Input DAT (referenced to CLK-DDR mode)  |                      | <u>I</u> | -1   | l .  |                              |

| Input set-up time                       | t <sub>ISUddr</sub>  | 2.5      |      | ns   | CL≤20 pF                     |

| Input hold time                         | t <sub>IHddr</sub>   | 2.5      |      | ns   | CL≤20 pF                     |

| Outputs DAT (referenced to CLK-DDR mod  | le)                  | L        | ·    | l .  |                              |

| Output delay time during data transfer  | t <sub>ODLYddr</sub> | 1.5      | 7    | ns   | CL≤20 pF                     |

| Signal rise time(DAT0-7) <sup>(2)</sup> | t <sub>RISE</sub>    |          | 2    | ns   | CL≤20 pF                     |

| Signal fall time (DAT0-7)               | t <sub>FALL</sub>    |          | 2    | ns   | CL≤20 pF                     |

[Table 11] Dual data rate interface timings

- NOTE 1. CLK timing is measured at 50% of VDD.

- NOTE 2. Inputs DAT rising and falling times are measured by min  $(V_{IH})$  and max  $(V_{IL})$ , and outputs CMD, DAT rising and falling times are measured by min  $(V_{OH})$  and max  $(V_{OL})$

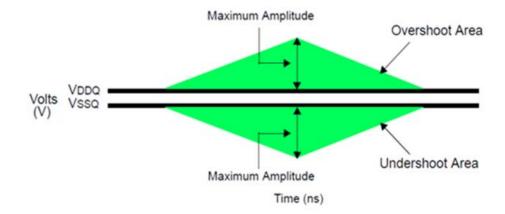

# 5.2 Bus signal

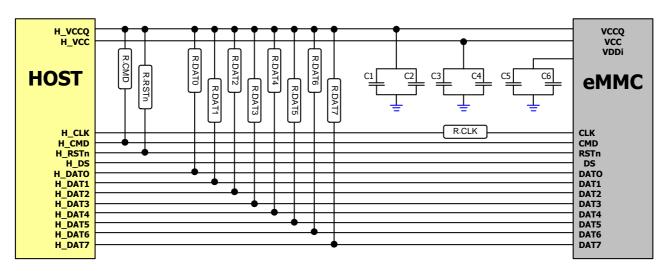

### 5.2.1 Bus signal line load

The total capacitance  $C_L$  of each line of e-MMC bus is the sum of the bus master capacitance  $C_{HOST}$ , the bus capacitance  $C_{BUS}$  itself, and the capacitance  $C_{Device}$  of the eMMC connected to this line, and requiring the sum of the host and bus capacitances not to exceed 20 pF.

$$C_L = C_{HOST} + C_{BUS} + C_{Device}$$

| Parameter                                  | Symbol              | Min | Тур | Max | Unit | Remark                                                                                                                                   |

|--------------------------------------------|---------------------|-----|-----|-----|------|------------------------------------------------------------------------------------------------------------------------------------------|

| Pull-up resistance for CMD                 | R <sub>CMD</sub>    | 4.7 |     | 100 | Kohm | to prevent bus floating                                                                                                                  |

| Pull-up resistance for DAT0-7              | R <sub>DAT</sub>    | 10  |     | 100 | Kohm | to prevent bus floating                                                                                                                  |

| Internal pull up resistance<br>DAT1 - DAT7 | R <sub>int</sub>    | 10  |     | 150 | Kohm |                                                                                                                                          |

| Bus signal line capacitance                | C <sub>L</sub>      |     |     | 30  | pF   | Single Device                                                                                                                            |

| Single Device capacitance                  | C <sub>DEVICE</sub> |     |     | 6   | pF   |                                                                                                                                          |

| Maximum signal line inductance             |                     |     |     | 16  | nH   | f <sub>PP</sub> ≤ 52 MHz                                                                                                                 |

| VDDi capacitor value                       | C <sub>REG</sub>    | 0.1 |     |     | uF   | To stabilize regulator output when target device bus speed mode is either backward-compatible, high speed SDR, high speed DDR, or HS200. |